Введение

Современные САПР цифровых систем (ЦС) предоставляют наряду с возможностью схематического проектирования, разработку ЦС при помощи языков аппаратного проектирования (HDL). К числу достоинств разработки ЦС с использованием языков аппаратного проектирования относят:

ü сокращение времени цикла разработки и производства конечного устройства;

ü гибкие возможности устранения возможных ошибок в процессе проектирования;

ü возможность применения сторонних или ранее разработанных аппаратных модулей;

ü легкость при формировании сводной документации устройства для стандартов описания по ISO9001 и специфическим внутренним стандартам документирования организации заказчика/разработчика.

Наряду с преимуществами использования вариативных методов проектирования, современные САПР ЦС позволяют, в зависимости от потребностей заказчика, реализовать ЦС на основе устройств на «жесткой логике», интегральной схеме (ИС) не способной менять собственную логическую организацию, или используя программируемые логические интегральные схемы (ПЛИС), ИС с программируемой логической организацией. ПЛИС обладают следующими преимуществами перед ИС на «жесткой логике»:

ü высокое быстродействие (до 700 МГц);

ü возможность перепрограммирования в конечном устройстве;

ü высокая степень интеграции, за счет разработки ЦС на одном кристалле;

ü возможность малосерийного производства специализированных ЦС.

Таким образом, разработка ЦС с использованием ПЛИС средствами языков аппаратного проектирования актуальна уже сегодня [2].

Реализация микропроцессора STACK CPU

Рассмотрим случай разработки вычислительного устройства (ВУ) на примере cтекового микропроцессора в САПР WEB ISE 11.1 на отладочной плате DIGILENT NEXYS 2 с ПЛИС Spartan 3E-500.

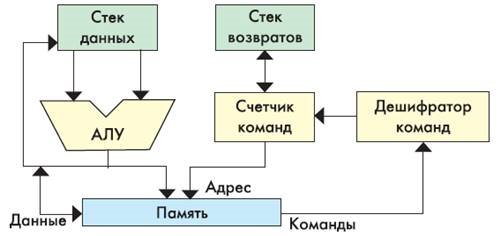

Рис. 1. Блок-схема стекового микропроцессора

Стековым процессором называется процессор, в качестве источника операндов и назначения результатов команд, исполняемых арифметически-логическим устройством (АЛУ) используется стек, а не регистр. Стек (англ. stack — стопка) — структура данных с методом доступа к элементам LIFO (англ. Last In — First Out, «последним пришел — первым вышел». При использовании стека машинная команда процессора не требует указания источника операндов и назначения (в канонической стековой архитектуре) в машинной команде, что позволяет применять для программирования стекового микропроцессора 0-операндные команды [1]. Применение 0-операндных команд в сочетании с основными особенностями стековой архитектуры процессора дают возможность[3]:

- упростить дальнейшее совершенствование ЦС за счет обработки рабочего слова процессора (упаковка, переупорядочивание и пр.), как на аппаратном, так и на программном уровне (компилятор);

- значительно уменьшить энергопотребление процессора при сохранении высокой производительности (до 40 и более раз), за счет упрощения внутренней архитектуры процессора;

- увеличить плотность кода, что позволяет значительно уменьшить себестоимость ЦС за счет уменьшения объема требуемого ОЗУ и КЭШа команд.

Вышеперечисленные достоинства стали причинной широкого применения стековых микропроцессоров во встраиваемых высокопроизводительных системах реального времени (системы, реагирующие в предсказуемое время на непредсказуемое появление внешних событий). Недостатком стековой архитектуры является сложная модель программирования, требующая высокой квалификации программиста.

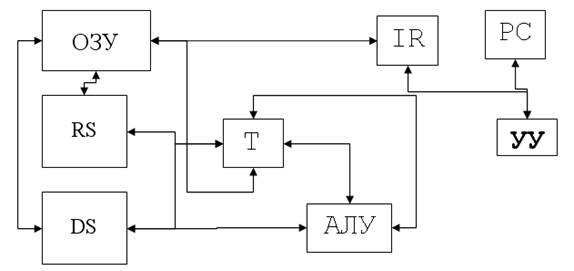

За основу стекового микропроцессора был использован проект процессора MSL16 Philip Leong [4], переданный автору в результате личной переписки на правах любых модификаций. Исходный проект был перепрофилирован с целью более эффективного использования внутренних особенностей семейства ПЛИС Spartan-3e. Был изменен механизм обращения к ОЗУ с целью использования скоростного потенциала синхронного обращения SDRAM. STACK CPU 3 представляет собой процессор:

- с двумя 16-битными стеками данных DS и адреса RS (возврата);

- T-регистр содержащий верхний элемент стека;

- IR-регистр содержащий четыре 4-х битных инструкции для выполнения;

- PC-регистр счетчик команд содержащий адрес следующей команды на исполнение.

Процедура выполнения команды следующая: извлечение элемента из T-регистра и любого из стеков DS или RS, выполнение операции и возврат результата в T. Структура команд позволяет любые четыре команды (за исключение вызова - CALL) упаковать в одно процессорное 16-битное слово и выполнить. Это позволяет значительно увеличить производительность, уменьшить количество обращений к ОЗУ и увеличить плотность кода (число команд на единицу информации).

Рис. 2. Структурная схема микропроцессора STACK CPU

Таблица 1

Набор инструкций процессора STACK CPU

|

Мнемоническая форма |

Машинный код |

Описание |

|

NOP |

0000 |

«Холостая» операция |

|

AND |

0001 |

T&=DS, pop DS |

|

XOR |

0010 |

T=T(XOR) DS, pop DS |

|

+ |

0011 |

T+=DS, pop DS |

|

0= |

0100 |

T= -1 if(T==0) else T=0 |

|

LIT |

0101 |

Push T to DS and load a value to T |

|

2DIV |

0110 |

T/=2 |

|

- |

0111 |

T=DS-T, pop DS |

|

DUP |

1000 |

Push T to DS |

|

DROP |

1001 |

Pop DS |

|

GOTO |

1010 |

Jump to T if T!=0 |

|

R> |

1011 |

Pop T to DS, pop RS to T |

|

>R |

1100 |

Pop T to RS, pop DS to T |

|

LOAD(@) |

1101 |

Загрузить из памяти mem[T] в регистр T |

|

SAVE(!) |

1110 |

сохранить в память по адресу mem[T] содержимое T-регистра |

|

SWAP |

1111 |

Поменять местами содержимое T и DS |

|

CALL |

10000 |

PUSH PC to RS, jump to T |

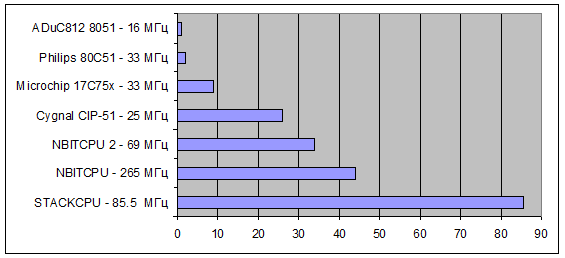

Набор команд соответствует принятому в языке Forth, применяемом при программировании встраиваемых систем реального времени и процессоров цифровой обработки, характеризующийся высокой плотностью и переносимостью кода. Пиковая производительность процессора STACKCPU составляет 85.5 миллиона инструкции или 85.5 MIPS.

Сравнение производительности с ранее разработанными автором микропроцессорами NBITCPU 1-2 [2] и коммерческими процессорами представлено ниже на рис. 3.

Рис. 3. Сравнение пиковой производительности NBitCpu 1-2, Stack CPU

и других микропроцессоров

В качестве аппаратной основы процессора STACK CPU используется отладочная плата

DIGILENT NEXYS 2 Spartan 3E-500 содержащая:

ü ПЛИС на 500 тыс. логических вентилей;

ü 16 Мбайт ОЗУ фирмы Micron и 16 Мбайт флэш-памяти Intel;

ü кварцевый осциллятор на 50 МГц, так же имеется возможность установки стороннего осциллятора;

ü 8 переключателей, четыре 7-ми сегментных светодиодных дисплея, 4 клавиши, USB-порт с максимальной передачей 38 Мбайт/с, PC/2 порт для подключения клавиатуры или мыши, VGA выход с разрешением 640х480 и 256 цветах, один RS232-порт с максимальная скорость приема/передачи 9600 Кбит/с;

ü разъем Hirose FX-2 для 100 МГц коммутации периферийных элементов;

ü четыре блока Pmod 2х6 контактов для подключения датчиков и устройств управления шаговыми двигателями.

Наличие развитой системы интерфейсов ввода-вывода у DIGILENT NEXYS 2 позволяет на основе процессора STACK CPU реализовать ЦС специального назначения.

Заключение

Таким образом, разработанный в САПР WEB ISE стековый микропроцессор STACK CPU обладает сравнительно большой производительностью, в сочетании с высокой плотностью кода рабочего слова процессора и затратах около 19% логических вентилей кристалла ПЛИС (3 млн. транзисторов). Оценка производительности на отладочной плате NEXYS 2 Spartan 3E-500, подтверждает эффективность разработки ЦС при помощи современных средств аппаратного проектирования, а именно ПЛИС XILINX Spartan 3e-500 и языка аппаратного проектирования VHDL.

Литература

- Каршенбойм И.Г. Стековые микропроцессоры, или новое – это хорошо забытое новое//Компоненты и технологии. 2003. № 9.

- Усатюк В.С. Отчет о создании скалярного микропроцессора с симметричной регистровой архитектурой на основе ПЛИС семейства SPARTAN-3E средствами языка аппаратного проектирования VHDL /В.С. Усатюк // Молодой ученый. ISSN 2072-0297 – 2009. - №6 – стр. 13-16

- Koopman P. Stack Computer: The New Wave. Ellis Horwood, New York, NY, USA, 1989. Режим доступа: [http://www.cs.cmu.edu/ ~koopman/index.html]

- Leong P.H.W.A FPGA Based Forth Microprocessor. Proceedings of the IEEE Symposium on Field-Programmable Custom Computing Machines (FCCM). Napa Valley, California USA, 1998.