In this article examined questions of designing and working out of a heterogeneous hardware-software complex - the universal computing accelerator are considered, allowing to realise «logic reflexion» executed algorithm in a FPGA.

В работе рассматриваются вопросы проектирования и разработки гетерогенного программно-аппаратного комплекса – универсального вычислительного ускорителя, позволяющего реализовывать «логическое отражение» исполняемого алгоритма в кристалл программируемой логической интегральной схемы (ПЛИС, FPGA).

Введение

… время собирать камни

Царь Соломон, Екклесиаста 3;5.

Общепринятой концепцией построения ключевых узлов ЭВМ (процессора, элементов системной и периферийной логики, различных типов памяти) стало применение стационарной архитектуры, тогда как код, исполняемый на ЭВМ, несет в себе большую изменчивость в силу широты класса решаемых задач. Именно необходимость преодоления этого противоречия обусловила дифференциацию компонентной базы ЭВМ, а именно возникновение плат расширения со специализированной под определенную задачу архитектурой: видеокарт, звуковых плат, плат физических эффектов и других компонентов.

C точки зрения экономической целесообразности, наиболее эффективной организацией ЭВМ является централизованная динамическая модель.

Централизованная динамическая модель подразумевает наличие одного полупроводникового элемента, содержащего большую часть элементов ЭВМ, также называемого «системой-на-кристалле»( System On Chip, SOC), которая обладает возможностью смены архитектуры на более оптимальную для текущего класса исполняемых алгоритмов.

До недавнего времени создание вычислительных систем с динамической архитектурой сдерживалось постоянным ростом производительности традиционных вычислительных систем. Но по мере замедления роста разрешающей способности технологий производства полупроводниковой техники (величины минимального размера одного логического элемента на кристалле полупроводника) развитие альтернативных архитектурных подходов стало актуальным направлением.

Примером реализации высокопроизводительных вычислительных систем на основе средств гибкой логики является суперкомпьютер XD-1 корпорации Cray, сочетающий в себе набор ПЛИС Virtex II Pro и процессоры Opteron [1].

Реализацией таких систем на основе ПЛИС занимается альянс FHPCA (FPGA High Performance Computin Alliance, альянс высокопроизводительных вычислений на основе ПЛИС). Например, им разработана система Maxwell с тороидально-петлевой организацией связей между объединением 32 «Блэйд-серверов», каждое из которых содержит один процессор Xeon и две PCI-E карты на ПЛИС Virtex4 от двух производителей Alpha Data и Nallatech [4]. Данная система для ряда задач вычислительной математики, например решения дифференциальных уравнений методом Монте-Карло, показала 250-1000-кратный прирост производительности по сравнению с аналогичной системой, не применяющей ПЛИС. Но представленные решения являются закрытыми и дорогими. Целью представленной работы является создание системы со свободно-распространяемым исходным кодом, не привязанным к аппаратным семействам ПЛИС, что обеспечит простоту расширения и низкую себестоимость универсального вычислительного ускорителя.

Особенности реализации универсального вычислительного ускорителя

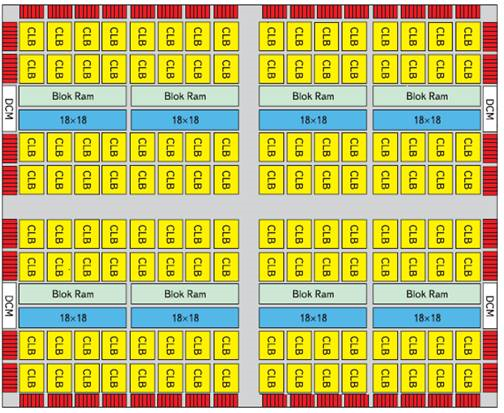

Основным элементом универсального вычислительного ускорителя является ПЛИС. Структура предполагаемого для разработки ПЛИС семейства SPARTAN-3E представлена ниже на рис. 1.

На кристалле расположены:

- CLB – конфигурируемые логические блоки (КЛБ), представляющие собой матрицу элементов логического И, программируемую или фиксируемую матрицу элементов логического ИЛИ;

- DCM- элементы цифрового управления синхросигналом;

- блоки аппаратного умножения 18х18 разрядных операндов;

- Block Ram – блочная память используемая для реализации ОЗУ, используемая при организации цифровой обработки совместно с расположенными рядом аппаратными умножителями;

-  сигнальные линии ввода-вывода по краям кристалла (условно говоря, так как, современный форм-фактор исполнения интегральных схем BGA).

сигнальные линии ввода-вывода по краям кристалла (условно говоря, так как, современный форм-фактор исполнения интегральных схем BGA).

Рис. 1. Структурная организация кристалла ПЛИС семейства SPARTAN-3E

При использовании ПЛИС в качестве аппаратной основы универсального вычислительного ускорителя нужно учитывать основные недостатки ПЛИС по сравнению со специализированной для решения конкретной задачи интегральной схемой(ASIC) ([2], [3]):

- низкая скорость перепрограммирования связей (до нескольких секунд для устройств с десятком миллионов конфигурируемых ячеек, вследствие параллельной загрузки данных малой ширины, 8 бит);

- отсутствие возможности частичного перепрограммирования (даже при незначительном изменении в конфигурации приходится перепрограммировать устройство целиком);

- программируемые внутренние соединения обладают большими задержками, чем реализованные аппаратно;

- невозможность обеспечить 100-процентное использование ресурсов ПЛИС.

Наряду с недостатками, ПЛИС обладает рядом важных достоинств ([2], [3]):

- неограниченное число изменения логической организации КЛБ;

- большое количество выделенных ресурсов (блоки синхронизации памяти, умножители), что дает возможность организовывать параллельные вычисления, распределенные по кристаллу ПЛИС. Это позволяет достигать лучших показателей производительности и цены, даже по сравнению с цифровыми сигнальными процессорами (DSP);

- Высокая устойчивость к помехам и большая простота разработки, что позволяет относительно просто добиться высоких рабочих частот и работы шины при большой разрядности.

Таким образом, в качестве сфер применения разрабатываемого устройства можно выделить ([5], [6]):

- реализацию динамически изменяемых высокопроизводительных аппаратных блоков исполняющих все многообразие алгоритмов слабо распараллеливаемых и/или не масштабируемых, обладающих мелко- и средне зернистым параллелизмом. Именно такие алгоритмы ограничиваю производительность современных ЭВМ;

- аппаратную реализацию устройств «физических интерфейсов», к которым сейчас относится большинство сетевых адаптеров, контроллеров, принтеров и сетевых плат и других устройств с целью уменьшения нагрузки на ЦП.

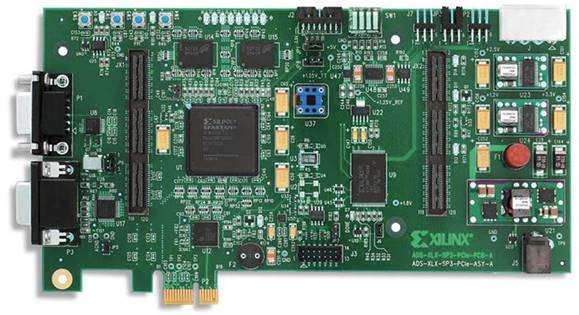

В качестве аппаратной основы разработки универсального вычислительного ускорителя будет использоваться отладочная плата Spartan 3 PCI Express Starter Kit, рис. 2.

Рис. 2. Отладочная плата Spartan-3 PCI Express Starter Kit

Отладочная плата Spartan-3 PCI Express Starter Kit содержит:

- ПЛИС XXILINX Spartan-3 (XC3S1000-4FG676C);

- кварц 50МГц, видео ЦАП;

- PCI Express X1 Card Edge с пропускной способность 0.5 Гб/с;

- память загрузки XCF08P-VO20C, DDR SDRAM память - 32MBx32;

- интерфейс PHILIPS PCI Express SerDes PX1011A, VGA интерфейс;

- последовательный порт RS-232, JTAG разъём;

- четыре переключателя Slide Switches, восемь пользовательских светодиодов;

- разъемы питания от внешнего источника или БП ПК.

В качестве САПР выбрана XILINX WEB ISE 11.1. При проектировании устройства будут использоваться языки аппаратного проектирования SystemC версии 2.0, VHDL 1993. Одной из планируемых задач является создание комплекса: сетевая плата – «физический интерфейс» D-Link DGE-528T и универсальный физический ускоритель, назначением которого станет уменьшение вычислительной нагрузки на процессор, в сочетании с реализацией аппаратного шифрования передаваемых данных [5].

Заключение

Развитие универсальных вычислительных ускорителей позволит, в дальнейшем, значительно увеличить производительность и «гибкость» применения вычислительных систем.

Литература

1. Кузьминский М. Cray, да не тот. Режим доступа: [свободный, http//www.osp.ru/os/ 2004/12/rub/1072570.html].

2. Максфилд К. Проектирование на ПЛИС. Курс молодого бойца. – М.: Издательский дом «Додэка-XXI»,2007. – 408 с.: илл.

3. Тарасов И. Системы на кристалле на базе FPGA Xilinx со встроенными процессорами PowerPC // Компоненты и технологии. 2005. №7.

4. Baxter R. Maxwell Режим доступа: [свободный, http://www.fhpca.org/maxwell.html]

5. Cheung O. Y. H. Implementation of an FPGA based Accelerator for Virtual Рrivate Networks. MPhil, 2002. Режим доступа: [свободный, http://www.cse.cuhk.edu.hk/~phwl/ mt/public/archives/students/yhcheung.pdf]

6. Leong N. M. P. FPGA Design Methologies for High Performance Applications. PhD, 2001. Режим доступа: [свободный, http://www.cse.cuhk.edu.hk/~phwl/mt/public/ archives/students/mpleong.pdf]