Введение

В настоящее время изделия микроэлектронной промышленности так широко вошли в современную жизнь общества, что отказ от них отбросил бы развитие цивилизации далеко назад. Мы все в большей степени зависим от эффективной работы различного рода радиоэлектронной аппаратуры (РЭА). Развитие микроэлектроники обусловлено постоянным ростом степени интеграции и функциональной плотности интегральных схем (ИС), что в свою очередь, если не улучшается конструктивно-технологические основы, приводит к росту возникновения отказов элементной базы РЭА и как следствие снижению ее надежности. Элементная база современных радиоэлектронных изделий состоит из высокоинтегрированных компонентов (интегральных схем, печатных плат). В связи с тем, что разработчики компонентов более высокой интеграции ИС делают разработку под общие для ряда предприятий требования к РЭА, а разработчики РЭА руководствуются конкретными техническими заданиями, возможно несовпадение требований к уровню качества компонентов РЭА. Таким образом, в различных организациях, выпускающих ИС, уровень их качества может различаться с требованиями к уровню качества этих компонентов для конкретного изделия РЭА. Основной тенденцией микроэлектроники последних лет является расширение функциональной сложности и повышение быстродействия ИС. Надежное функционирование РЭА требует специальных методов и средств отбраковки потенциально ненадежных компонентов ИС. Проблема диагностического контроля осложняется, поскольку функционально на один выходной контакт ИС приходится цепь, содержащая тысячи соединенных между собой электронных компонентов (ЭК), из которых каждый не испытывают. Поэтому результат берется суммарный. Контроль и анализ функциональных операций при обращении ИС должны достоверно характеризовать длительность их безотказной работы, что позволит создать не только высоконадежную РЭА, но и избежать ущерба, нередко исчисляемого человеческими жизнями.

Надежность интегральных схем

Один из основных показателей РЭА - надежность - зависит как от надежности используемой элементной базы, так и от принятых схемотехнических и конструкторских решений. Учитывая значимость современной аппаратуры в человеческой деятельности, требования к надежности аппаратуры постоянно повышаются. Это связано с тем, что от правильной работы РЭА зависят ход выполнения технологического процесса, достоверность получения результатов измерений и обработки данных, и т.п. Вопросам повышения надежности РЭА на всех этапах ее проектирования и производства уделяется самое большое внимание.

Надежность, как сочетание свойств безотказности, ремонтоспособности, долговечности и сохраняемости, и сами эти качества количественно характеризуются различными функциями и числовыми параметрами. Правильный выбор количественных показателей надежности РЭА позволяет объективно сравнивать технические характеристики различных изделий как на этапе проектирования, так и на этапе эксплуатации (правильный выбор системы элементов, технические обоснования работы по эксплуатации и ремонту РЭА, объем необходимого запасного имущества и др.) [1,2].

На сегодняшний день значительную часть элементно-компонентной базы РЭА составляют цифровые изделия - интегральные схемы такие как: микропроцессоры, микроконтроллеры, аналого-цифровые преобразователи и т.д. В связи с этим надежность РЭА целесообразно сопоставить с надежностью цифровых изделий, подверженных катастрофическим отказам.

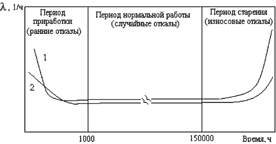

Зависимость интенсивности отказов от времени работы ИС имеет вид кривой (называемой иногда "ванной", рисунок 1), которая характеризуется тремя периодами: периодом приработки (называемого иногда периодом "детских" или ранних отказов), в котором интенсивность отказов вначале велика, а затем быстро падает; периодом нормальной работы, в котором значение интенсивности отказов постоянно, и периодом старения (примерно через 25-30 лет нормальной работы), в котором интенсивность отказов начинает вначале медленно, а затем более быстро возрастать. Однако, данная стадия у ИС только предполагается.

Рис. 1. Типовая зависимость интенсивности отказов ИС от времени: 1 - без отбраковочных испытаний; 2 - с проведением отбраковочных испытаний

Ранние отказы возникают, как правило, вследствие конструктивных и технологических недостатков. В нормальных условиях работы этот период длится до 1000 ч. или примерно 6 недель. На окончание этого этапа указывает выравнивание кривой интенсивности отказов. Интенсивность отказов в период приработки имеет тенденцию к уменьшению по мере усовершенствования конструкции и технологии [3]. Однако, согласно работе [4], при уменьшении топологических норм проектирования, резко сокращается период нормальной работы ИС (рисунок 2).

Рис. 2. Зависимость периода нормальной работы от топологических норм проектирования

В настоящее время общеприняты два основных направления увеличиния надежности выпускаемых полупроводниковых изделий (ППИ) и ИС:

- устранение причин отказов при изготовлении изделий путем изучения, усовершенствования производственного процесса и повышения контроля, то есть воздействия на процесс производства посредством обратной связи передачи информации и создание в конечном счете бездефектной технологии;

- выявление и удаление изделий с отказами (действительными и потенциальными) из готовой партии до поставки потребителю.

Наиболее эффективным методом повышения качества и надежности выпускаемых изделий является первое направление. Отказы возможны даже в хорошо освоенном производстве. По этой причине распространенным способом повышения качества и надежности выпускаемой партии ПП и ИС (а не конкретно каждого изделия) является проведение отбраковочных испытаний на этапе выходного контроля этих партий на заводе изготовителе. Считается, что случайных отказов ППИ не бывает, каждый отказ имеет причину и является следствием приложения некоторой нагрузки. «Слабые» ППИ, которые остались невыявленными к началу эксплуатации, могут стать причиной отказов РЭА. Для того чтобы отбраковочные испытания были эффективными, нужно знать, какие нагрузки и как ускоряют появление отказов. Опыт показывает, что внедрение отбраковочных испытаний существенно повышает средний уровень их надежности (рис. 1) [5].

Таким образом, для повышения надежности цифровой ЭКБ РЭА необходимо использование двух методов: усовершенствование технологии и конструкции а так же проведение ускоренных испытаний. В свою очередь проведение ускоренных испытаний позволяет выявить отказы ИС связанные с конструктивно-технологическими факторами такими как: ошибки литографии; дефекты окисла, металлизации, контактов; короткие замыкания или обрывы в проводящих шинах а также между поликремнием и металлом; и т.д. Правильно понимать физическую природу и сущность отказов очень важно для обоснованной оценки надежности технических устройств.

Причины отказов ИС

На элементы РЭА постоянно воздействуют внешние и внутренние эксплуатационные факторы. К первым относятся температура, влажность, давление и химический состав окружающей среды, радиация, электромагнитные поля, механические нагрузки, возникающие при эксплуатации (вибрации, удары) и другие факторы, влияющие на элементы независимо от того, работают они или выключены. Ко вторым факторам относятся напряжения и токи установившихся переходных режимов работающих под нагрузкой элементов и возникающие в связи с этим выделение в элементе тепла, образование электрических и магнитных полей, механические нагрузки.

Из-за воздействия эксплуатационных факторов в материалах элементов протекают различные физико-химические процессы, изменяющие их свойства: диффузионные процессы в объеме и на поверхности; перемещение и скопление точечных дефектов и дислокаций в твердых телах; флуктуационные разрывы межатомных связей в металлах и сплавах; разрыв химических связей цепей макромолекул полимерных материалов; сорбционные процессы; электролитические процессы; сублимация материалов; действие поверхностно-активных веществ; структурные превращения в сплавах металлов и др. Скорость и характер протекания этих процессов определяется концентрацией основных веществ и примесей в материалах и уровнями энергетических воздействий на элемент эксплуатационных факторов.

Концентрация проникающих в материалы веществ и уровень энергетических воздействий зависят от качества защиты элемента от влияния внешних и внутренних эксплуатационных факторов. Возрастание интенсивности их воздействия на элемент увеличивает скорость протекания физико-химических процессов, в результате чего возникают обратимые и необратимые изменения в материалах.

Возникновение различных физико-химических процессов в материалах и скорость их протекания обусловлены уровнем воздействующих энергий: механической, тепловой, электрической, химической и связаны с превращением одного вида энергии в другой. Большинство процессов являются термически активируемыми процессами, т.е. они могут протекать только при определенном уровне тепловой энергии, причем интенсивность их увеличивается при нагревании элемента. Поэтому тепловая энергия часто играет определяющую роль в развитии физико-химических процессов в материалах элементов. Если уровни эксплуатационных нагрузок превышают допустимые для элемента значения, то это приводит к разрушению структуры его материалов и внезапному отказу. Существует принципиальная причинно-следственная связь последовательности или цепи событий, приводящих к отказам элементов. Так, воздействующие на элемент эксплуатационные факторы порождают физико-химические процессы в материалах, которые приводят к изменению свойств этих материалов. В результате этого изменяются параметры элемента и, когда хотя бы один из них выходит из строя, наступает отказ. В этой цепи предшествующее событие выступает как причина последующего события. Исходной же причиной отказов, движущей силой их проявления являются эксплуатационные факторы [6].

Таким образом, отказы ИС можно разделить на группы: отказы связанные с тепловой энергией и электрической.

Таблица 1

Виды отказов в зависимости от ускоряющего фактора

|

Ускоряющий фактор |

Вид отказа |

|

Температура |

Электромиграция |

|

Дефекты окисла выявленные температурой | |

|

Обрыв соединений вследствие образования интерметаллических соединений | |

|

Повышенное напряжение |

Дефекты окисла выявленные повышенным напряжением |

|

Времязависимый пробой диэлектрика |

Однако в процессе эксплуатации наблюдается корреляция отказов связанных с тепловой и электрической энергиями, поэтому изучение механизмов отказов необходимо для понимания влияния этих энергий на тот или иной вид отказа.

Механизмы отказов ИС

Доминирующие механизмы отказов в микроэлектронных устройствах основанных на кремнии, которые наиболее часто встречаются — это электромиграции (Electromigration (EM)), временной диэлектрический пробой (Time Dependent Dielectric Breakdown (TDDB)), температурная нестабильность напряжения обратного смещения (Negative Bias Temperature Instability (NBTI)) и инжекция горячих носителей (Hot Carrier Injection (HCI)). Другие модели деградации действительно существуют, но являются менее распространенными. Указанные механизмы механизмы главным образом можно классифицировать как стационарные (статистические, постоянные) виды отказов (EM и TDDB) и отказы по износу (NBTI и HCI) [7].

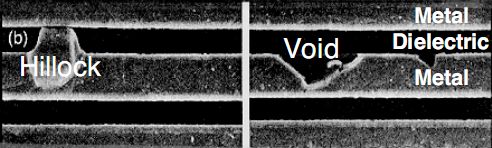

Электромиграция может привести к отказу межсоединений в ИС. Она характеризуется миграцией атомов металла в проводнике в направлении потока электронов. Электромиграция вызывает пустоты или лунки в некоторых участках проводника и соответствующие бугорки в других его частях рисунок 3 [8-9, 10].

Рис. 3. Электромиграции

Временной диэлектрический пробой наблюдается в виде формирования токопроводящих дорожек через подзатворный окисел к подложке, за счет потока туннелированных электронов. Если туннелирующий ток достаточен, это может привести к неустранимому повреждению окисла и окружающего материала. Это повреждение может привести к снижению производительности и возможному отказу устройства. Если туннелирующий ток остается очень низким, это увеличивает электрическое поле, для включения затвора и затрудняет его функциональные возможности. Хотя основные напряжения сократились с уменьшением размеров элемента, напряжение питания осталось неизменным. Эти усиленные поля доставляют еще больше проблем, так как высокие поля усиливают действия TDDB [10, 11].

Диэлектрический пробой вызывается токами утечки через микроскопические и макроскопические дефекты в окисле. Различают собственный (intrinsic) пробой, обусловленный стойкостью совершенного окисла, и привнесенный (extrinsic) пробой, зависящий от случайного наличия скрытых технологических дефектов (пылинка, микротрещина и т.п.) и слабых мест. Максимальное значение напряженности электрического поля в окисле SiO2 составляет (~ 107 В/см). Реальные рабочие электрические режимы работы приборов соответствуют приблизительно половине максимального (~5×106 В/см). В процессе функционирования прибора в окисле проходят процессы деградации, приводящие в конце концов к пробою при напряжениях, существенно меньших максимальных. Время жизни (срок службы) окисла по отношению к TDDB сильно зависит от электрического поля в окисле и рабочей температуры (рис. 4).

Рис. 4. Зависимость срока службы окисла от электрического поля

Для того чтобы предсказывать долговременное поведение окисла при относительно низких затворных напряжениях, проводятся ускоренные испытания при высоких затворных смещениях, и иногда – при повышенных температурах. Адекватность таких испытаний до сих пор в полной мере не установлена, как и невыясненным до конца остается вопрос о микроскопическом механизме временного пробоя. Ясно только, что пробой развивается в результате долговременных процессов «изнашивания» (wearout) окисла в условиях электрической нагрузки, которые, возможно, следует отделять от процессов старения (aging), происходящих просто при длительном хранении. Изнашивание является кумулятивным процессом и коррелирует с полным зарядом, протекающим через окисел за время электрической нагрузки. В частности, статистическая зависимость доли отказавших образцов в партии как функция полного заряда, прошедшего через окисел, определяется распределением Вейбулла. Считается, что процессы изнашивания при электрической нагрузке выражаются в накоплении неких дефектов, скорость образования которых определяется либо электрическим полем (Е-модели), либо током, протекающим через окисел (1/Е –модели) [17].

Температурная нестабильность напряжения обратного смещения возникает только в pMOS устройствах, в которых наблюдается повышенная температура из за приложенного напряжения обратного смещения на затвор. Деградация происходит в области подзатворного диэлектрика, позволяя электронам и дыркам быть пойманными в ловушку. Обратное смещение управляется меньшим электрическим полем, чем инжекция горячих носителей, что делает ее более существенной угрозой в технологиях с малыми размерами элементов, в которых увеличение электрических полей используют в сочетании с меньшими длинами затвора. Область воздействия ловушек образованных NBTI оказывается более выраженной в более тонких окислах [12-13; 10].

Эффект NBTI проявляется тогда, когда в процессе работы ИС pМОП транзистор полностью открывается и происходит зарядка нагрузочной емкости. Так как при этом транзистор смещен отрицательным напряжением затвор-исток, эффект получил название “температурная нестабильность при отрицательном смещении”.

Эффект HCI проявляется только в моменты переключения, тогда как NBTI влияет на схему значительно дольше – пока на затвор pМОП транзистора не будет подан запирающий сигнал. При этом схема находится в статическом состоянии, и никаких переключений не происходит. NBTI в основном влияет на pМОП транзисторы, как правило приводя к изменению их порогового напряжения (Vth) примерно на 50мВ за 10-летний срок службы, то есть примерно на 25-30%.

Когда на затвор pМОП транзистора подано обратное смещение (Vgs = - Vdd), на границе подзатворного окисла и канала происходит распад связей Si-H, что влечет за собой генерацию поверхностных ловушек. Скорость генерации таких ловушек возрастает с ростом температуры, а также при увеличении времени нахождения транзистора в режиме обратного смещения. Поверхностные ловушки приводят к росту порогового напряжения (|Vth|) pМОП транзисторов. Это, в свою очередь, приводит к увеличению задержки схемы, и, когда деградация задержки достигает определенного предела, схема перестает удовлетворять временным ограничениям. В целом, на долю NBTI приходится около 20% ухудшения быстродействия и, в худших случаях, функциональных сбоев в работе схемы. Однако экспериментально доказано, что когда транзистор закрывается, количество поверхностных ловушек начинает сокращаться. Следовательно, влияние NBTI на pМОП транзистор зависит от времени, проведенного им в режиме перенапряжения [22].

Инжекция горячих носителей возникает как в nMOS так и в pMOS устройствах подверженных напряжению смещения на стоке. Высокие электрические поля возбуждают носители (электроны или дырки), которые инжектируют (проникают) в область подзатворного диэлектрика (рисунок 5). Как и в случае NBTI, ослабленный подзатворный диэлектрик может с большей вероятностью захватить электроны или дырки, вызывая изменения в пороговом напряжении, которое в свою очередь приводит к изменению в субпороговом токе утечки. Вероятность HCI увеличивается с увеличением напряжения смещения и является преобладающим механизмом при более низких температурах напряжения [14, 10]. Поэтому, повреждения от горячих носителей, в отличии от других механизмов отказа, не будет ускоренно испытаниями на срок службы при повышенных температурах (High Temperature Operating Life (HTOL)), которые обычно используют для форсирования испытаний на долговечность [15].

Рисунок 5 Инжекция горячих носителей

Исследования, проведенные в работе [16], показали, что усовершенствование материала проводника, сделанное в 0.18 мкм технологии, в дальнейшем уменьшило эффект электромиграции. Результирующая тенденция показывает сокращение интенсивности отказов из-за электромиграции. Однако, с уменьшением размеров элементов, эффекты износа инжекции горячих носителей и нестабильности напряжения обратного смещения становятся более распространенными

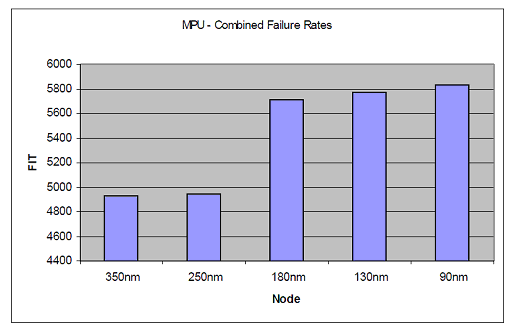

На рисунке 6 показан комбинированный график интенсивности отказов для устройств микропроцессорного типа. Этот график показывает, что для интенсивности отказов существенна зависимость от топологических норм. Устройства микропроцессорного типа яркий пример этой тенденции, так как электрические и термические условия этих частей соответствуют каждой технологии.

Рисунок 6 Интенсивность отказов для устройств микропроцессорного типа

По мере развития технология переходит к меньшим размерам элементов, при этом напряжение оперативного тока устройств не уменьшается пропорционально толщине подзатворного диэлектрика, что приводит к более высокому электрическому полю; кроме того, увеличение плотности транзисторов на чипе, вызывает большую мощность рассеяния и в свою очередь увеличивает рабочую температуру посредством самонагрева. Меньшие по размеру и наиболее быстрые схемы обладают повышенной плотностью тока, низкой устойчивостью к напряжению и высокому электрическому полю, что делает их более уязвимыми к отказам связанным с электричеством. Новые устройства с новым проектными нормами и материалами требуют, чтобы анализ отказов нашел новые модели для отдельных механизмов отказов, а также возможность взаимодействия между ними. [16].

Ускоренные испытания ИС

В настоящее время для определения времени наступления периода старения ИС, то есть их долговечности, остаётся практически единственный способ — проведение ускоренных испытаний, при которых ИС работают в условиях более высоких нагрузок, чем при нормальной эксплуатации. Результаты, полученные при повышенных нагрузках, экстраполируют на нормальные условия эксплуатации. Цель ускоренных испытаний ИС на долговечность заключается в том, чтобы старение ускорилось, а процесс деградации параметров происходил так же, как и при нормальной работе схемы [3].

Известно, что отказы возможны даже в хорошо освоенном производстве. По этой причине распространенным способом повышения качества и надежности выпускаемой партии ППИ и ИС (а не конкретно каждого изделия) является проведение отбраковочных испытаний на этапе выходного контроля этих партий на заводе-изготовителе[5].

Возможны четыре типа процедур контроля качества ППИ на входном контроле:

- проведение 100% приработки изделий, электротермотренировки (ЭТТ), для обнаружения и отбраковки «отказов начального периода наработки», использование изделий, выдержавших успешно такую приработку;

- проведение 100% приработки изделий (в обоих случаях она проводится при полной нагрузке и повышенной температуре окружающей среды) и после нее – дополнительных выборочных испытаний от партии на срок службы или испытаний при повышенной температуре (85°С) и повышенной относительной влажности (85%);

- проведение только выборочных испытаний с целью оценки годности партии изделий методами ускоренных испытаний;

- проведение испытаний в более щадящих условиях, чем выборочные испытания, но вместе с тем полнее, в более близких к реальным условиям эксплуатации, чем при испытаниях изделий по ТУ [18].

Срабатывание механизмов отказов ИС в большинстве случаев ускоряется под воздействием температуры и напряжения или тока, поэтому в процессе тренировки ИС должны работать при максимально допустимом напряжении и максимально возможной температуре.

ЭТТ является эффективным средством ускорения срабатывания эксплуатационных механизмов отказов. Она дает много информации за короткое время, но достоверные результаты можно получить на основе правильного выбора электрических и тепловых нагрузок, выявления видов и механизмов отказов, соответствующих начальным условиям эксплуатации, а также статистической обработки полученных результатов.

В реальных условиях эксплуатации ИС чаще всего работают периодически, то есть подвергаются внезапному включению электрического режима, а затем внезапному его выключению. Замечено, что зачастую ИС надежно работают в постоянно включенном режиме, но их надежность падает в зависимости от того, как часто режим включается и выключается. Поэтому в последние годы стал широко использоваться при электротренировке прерывистый режим, то есть циклическое изменение электрических воздействий «включено/выключено» — режим энергоциклирования [19].

В производственной практике долговечность ИС определяют по результатам статической или динамической электротермотренировки (ЭТТ), позволяющей выявлять отказы ИС с разной энергией активации. Наибольшее распространение получили два варианта, а именно:

- при предельных электрических нагрузках (обычно 30% от номинального) и предельной температуре (125–150°С), при допущении корреляции с результатами эксплуатации при температуре 55°С, при времени испытаний в целом не более 1000 ч.(в зарубежной аббревиатуре HTOL - High Temperature Operating Life Test, метод 1005, 1006 по MIL-STD 883C);

- при температурах, физически допустимых конструкцией ИС (200–300°С), продолжительностью 48–100 ч. и более(максимально 1000 или 4000 ч.).

К первому варианту испытаний можно отнести все виды электротермотренировок [3].

Расчет надежности ИС

В работах [16; 20] показано, что JDEC (Joint Experimental development of Electronic Components) стандарт номер 47D “Stress-Test-Driven Qualification of Integrated Circuits”, определяет типичный способ ускоренных испытаний, основанный на испытании срока службы при повышенных температурах (HTOL испытаниях). Продолжительность испытаний 1000 часов при температуре +125°C. Заявленное предназначение HTOL тестирования – имитация работы устройства при повышенных температурах и напряжениях, выше чем номинальные рабочие напряжения для обеспечения достаточного ускорения имитации многих лет эксплуатации при температуре окружающей среды (типично +55°C). Данные полученные из HTOL испытаний традиционно переводят на более низкую температуру используя ускоряющую температурную модель Аррениуса:

Где:

Ea – энергия активации в электронвольтах (еВ);

K – постоянная Больцмана (8.62×10-5 еВ/К);

Ttest – абсолютная температура испытания (K);

TField – абсолютная температура системы (К);

ΛTest – интенсивность отказов при температуре тестирования;

ΛField – интенсивность отказов при температуре реальных условий эксплуатации;

Таким образом, при прогнозировании интенсивности отказов используя результаты HTOL испытаний, необходимо знать Ea и TField. Энергия активации – параметр который используют, чтобы выразить степень ускорения, связанную с температурой. Отдельные механизмы отказов сопровождаются уникальным значением энергии активации (JEDEC публикация № 122B.). Тем не менее, традиционные методы используют энергию активации 0.7 еВ, ее принято считать средней энергией активации для механизмов отказов, которые происходит во время срока службы устройств. Этот срок службы лежит за пределами отказов во время приработки. В промышленности широко используют это значение энергии активации в следующих двух случаях:

- При оценке общей интенсивности отказов, не сосредотачиваясь на отдельных механизмах отказов. Предполагается постоянное значение в отношении комбинации энергий активации отдельных механизмов.

- Когда механизмы отказа неизвестны.

Цель HTOL состоит в том, чтобы получить максимально возможное ускорение, чтобы получить максимальное эквивалентное время работы, с нулевыми отказами. Принятие более высоких энергий активации будет служить этой цели, но уменьшит верхний предел интенсивности отказов. Например, принятие энергии активации 1.0 еВ вместо 0.7 еВ поднимает ускоряющий фактор до 504 вместо 78 (в 6.5 раз больше). С другой стороны интенсивность отказов уменьшится от 51 FIT до 8 FIT, которые еще более оптимистичны см. таблицу 2.

Таблица 2

Сравнение методов расчета интенсивности отказов

|

Part Number |

Field Failure Rate |

Predicted Failure Rate |

HTOL Failure Rate (0.7 eV Act. Energy) |

HTOL Failure Rate (1.0 eV Act. Energy) |

|

MT16LSDF3264HG |

689 |

730 |

51 |

8 |

|

M470L6524DU0 |

415 |

418 |

51 |

8 |

|

HYMD512M646BFS |

821 |

1012 |

51 |

8 |

|

MC68HC908SR12CFA |

220 |

249 |

51 |

8 |

|

RH80536GC0332MSL7EN |

144 |

291 |

51 |

8 |

Таким образом, стандартные HTOL испытания не должны использоваться для прогнозирования интенсивности отказов, так как они дают оценки, которые являются слишком низкими. Это связанно с двумя ограничениями для стандартных HTOL испытаний: множество механизмов отказов и предел нулевых отказов.

Ограничения множества механизмов отказов: в идеале, но не реально, полное распределение срока службы ИС рассматривать под фиксированным набором ускоряющих условий для того чтобы сделать уверенный вывод о надежности. Одни ускоряющие испытания, такие как HTOL, не могут стимулировать все основные механизмы отказов (такие как HCI), и ускоряющий фактор, полученный от некоторых из них, незначителен. Если HTOL испытания выполнены при произвольном напряжении и температуре для ускорения основанного только на одном механизме отказа, тогда только этот механизм будет разумно ускорен. В этом случае, который справедлив для большинства устройств, отчет о интенсивности отказов FIT (особенно основанный на нулевых отказах), будет бессмыслен по отношению к другим механизмам отказов.

Нулевые отказы: Факт, что нулевые отказы HTOL испытаний ограничивают статистическую достоверность прогнозирования интенсивности отказов. Нулевые отказы HTOL испытаний – недостаточный показатель ожидаемой интенсивности отказов. Чтобы получить статистическую достоверность, отказы должны наблюдаться [16].

Специалисты фирмы Analog Devices считают, что 1000 ч. испытаний при 125°С эквивалентно 10 годам при температуре 55°С.

Далее представлены данные по надежности изделий фирмы Analog Devices. Данные взяты с сайта фирмы из отчета по надежности от 12.04.2012 года и представлены в виде таблиц результатов расчета интенсивности отказов для различных технологий при различной температуре.

Технология 0,25 мкм CMOS

|

T = 55°С | |

|

0.25um CMOS Life Test Data Summary | |

|

Overall Sample Size |

9427 |

|

Qty. Fail |

0 |

|

Equivalent Device Hrs. @ 55 deg C) |

1358653213 |

|

FIT Rate (60% CL, 55 deg C) |

0.67 |

|

MTTF (60% CL, 55 deg C) |

1482776428 |

|

FIT Rate (90% CL, 55 deg C) |

1.69 |

|

MTTF (90% CL, 55 deg C) |

590056898 |

|

Calculations assumes 0.7 eV Activation Energy | |

|

T = 125°С | |

|

0.25um CMOS Life Test Data Summary | |

|

Overall Sample Size |

9427 |

|

Qty. Fail |

0 |

|

Equivalent Device Hrs. @ 125 deg C) |

17495239 |

|

FIT Rate (60% CL, 125 deg C) |

52.37 |

|

MTTF (60% CL, 125 deg C) |

19093561 |

|

FIT Rate (90% CL, 125 deg C) |

131.61 |

|

MTTF (90% CL, 125 deg C) |

7598103 |

|

Calculations assumes 0.7 eV Activation Energy | |

Технология 65 нм CMOS

|

T = 55°С | |

|

65nm CMOS Life Test Data Summary | |

|

Overall Sample Size |

1246 |

|

Qty. Fail |

0 |

|

Equivalent Device Hrs. @ 55 deg C) |

106566850 |

|

FIT Rate (60% CL, 55 deg C) |

8.6 |

|

MTTF (60% CL, 55 deg C) |

116302535 |

|

FIT Rate (90% CL, 55 deg C) |

21.61 |

|

MTTF (90% CL, 55 deg C) |

46281497 |

|

Calculations assumes 0.7 eV Activation Energy | |

|

T = 125°С | |

|

65nm CMOS Life Test Data Summary | |

|

Overall Sample Size |

1246 |

|

Qty. Fail |

0 |

|

Equivalent Device Hrs. @ 125 deg C) |

1372250 |

|

FIT Rate (60% CL, 125 deg C) |

667.73 |

|

MTTF (60% CL, 125 deg C) |

1497615 |

|

FIT Rate (90% CL, 125 deg C) |

1677.96 |

|

MTTF (90% CL, 125 deg C) |

595962 |

|

Calculations assumes 0.7 eV Activation Energy | |

Интенсивность отказов здесь рассчитывалась по формуле: Failure Rate = X²/ (2*N*H*At)

где: X² - кси квадрат распределение, значение которое зависит от количества отказов и доверительных интервалов; N – количество тестируемых образцов; H – время испытания; At – ускоряющий фактор (Ea = 0.7 eB T = 55°С); 125°C к 55°C, At = 77; Equivalent Device Hrs = N*H*At; MTTF = 1/ Failure Rate; FIT = Failure Rate*10-9

В работе [21] автор приводит таблицу значений X² для различных доверительных интервалов и числа отказов:

Таблица 3

Распределения X²

|

CL 60 % |

CL 90 % | ||

|

Число отказов |

Значение X² |

Число отказов |

Значение X² |

|

0 |

1.833 |

0 |

2.5 |

|

1 |

4.045 |

1 |

7.779 |

|

2 |

6.211 |

2 |

10.645 |

|

3 |

8.351 |

3 |

13.362 |

|

4 |

10.473 |

4 |

15.987 |

|

5 |

12.584 |

5 |

18.549 |

|

6 |

14.685 |

6 |

21.064 |

|

7 |

16.780 |

7 |

23.542 |

|

8 |

18.868 |

8 |

25.989 |

|

9 |

20.951 |

9 |

28.412 |

|

10 |

23.031 |

10 |

30.813 |

|

11 |

25.106 |

11 |

33.196 |

|

12 |

27.179 |

12 |

35.563 |

Возьмем одинаковое количество образцов (100 штук) изготовленных по различным технологиям, испытаем их в течении 1000 часов при температуре 125С. В этом случае EDH= 100*1000*77= 77*105. При нулевых отказах X² = 1.833 ( для доверительных интервалов CL 60%), FR = X²/2EDH, FIT = FR/10-9, FR= 1,833 /2*77*105 = 9*10-9 FIT = 9

Таблица 4

Данные расчета интенсивности отказов для различных технологий

|

Технология |

Температура |

Ускоряющий фактор |

X² |

EDH |

FIT |

|

0,35 мкм |

125 125 125 125 125 125 |

77 77 77 77 77 77 |

1,833 |

77*105 |

9 |

|

0,25 мкм |

1,833 |

77*105 |

9 | ||

|

0,18 мкм |

1,833 |

77*105 |

9 | ||

|

0,13 мкм |

1,833 |

77*105 |

9 | ||

|

90 нм |

1,833 |

77*105 |

9 | ||

|

60 нм |

1,833 |

77*105 |

9 |

Исходя из расчетов, интенсивность отказов в единицу времени (FIT) не зависит от технологии производства ИС. Таким образом, можно сделать вывод, что интенсивность отказов, рассчитанная по приведенному выше примеру, зависит только от количества испытуемых образцов, не принимая в расчет различия в технологии производства, механизмах отказов, ускоряющих факторах и т.д. Такой расчет интенсивности отказов, носит только количественный характер и не может в полной мере дать оценку, реальной надежности того или иного изделия. При определении надежности нужно учитывать как количество испытуемых образцов, так и их сложность, а также особенности связанные с материалами которые используются при их производстве, технологические нормы, различия в преобладающих механизмах отказов, для тех или иных тех. норм, разницу в энергии активации тех или иных отказов, а, следовательно, и значение ускоряющего фактора.

Согласно работе [3] существует множество различных документов по которым производят вычисления ускоряющего фактора. В каждом документе обозначены свои правила определения констант и температур переходов. Документ NTT procedure предусматривает один коэффициент ускорения для всех ИС, американский справочник MIL-HDBK 217 - 25 для разных технологий изготовления ИС, разделенных на 7 категорий. Документ CNET предусматривает разные коэффициенты ускорения для четырёх типов технологий и задаёт две разные константы для герметичных и негерметичных изделий. Процедура фирмы Siemens использует одни и те же константы для всех ИС, за исключением перепрограммируемых интегральных запоминающих устройств. Всё это приводит к тому, что температурные коэффициенты ускорения, вычисленные по разным методикам для одной и той же ИС, существенно отличаются.

Расчёты показывают, что значения коэффициентов ускорения для одной и той же ИС, работающей в одних и тех же условиях, в одинаковых корпусах (герметичном или не герметичном), уже при температурах порядка 100°С могут различаться более чем в 100 раз, в зависимости от того, по какому документу их рассчитывают. Эта разница увеличивается при повышении температуры. Весьма существенны и различия в интенсивностях отказов одной и той же ИС при разных температурах, определённые по разным документам. Для температуры 20°С для негерметичных корпусов они отличаются от 8 до 790 ФИТ, а для температуры 80°С - от 33 до 5648 ФИТ, то есть больше, чем на два порядка [3].

Выводы:

- На сегодняшний день значительную часть элементно-компонентной базы РЭА составляют цифровые изделия интегральные схемы такие как: микропроцессоры, микроконтроллеры, аналого-цифровые преобразователи и т.д. В связи с этим надежность РЭА целесообразно сопоставить с надежностью цифровых изделий.

- существует принципиальная причинно-следственная связь последовательности или цепи событий, приводящих к отказам элементов. Так, воздействующие на элемент эксплуатационные факторы порождают физико-химические процессы в материалах, которые приводят к изменению свойств этих материалов. В результате этого изменяются параметры элемента и наступает отказ. В этой цепи предшествующее событие выступает как причина последующего события. Исходной же причиной отказов, движущей силой их проявления являются эксплуатационные факторы.

- Доминирующими механизмами отказов в микроэлектронных устройствах основанных на кремнии, являются: электромиграции, временной диэлектрический пробой, температурная нестабильность напряжения обратного смещения и инжекция горячих носителей. Другие модели деградации действительно существуют, но являются менее распространенными.

- Новые устройства с новым проектными нормами и материалами требуют, чтобы анализ отказов нашел новые модели для отдельных механизмов отказов, а также возможность взаимодействия между ними. Понимание этих потенциальных взаимодействий особенно важно и требует серьезных исследований.

- В настоящее время для определения времени наступления периода старения ИС, то есть их долговечности, остаётся практически единственный способ — проведение ускоренных испытаний, при которых ИС работают в условиях более высоких нагрузок, чем при нормальной эксплуатации. Результаты, полученные при повышенных нагрузках, экстраполируют на нормальные условия эксплуатации. Цель ускоренных испытаний ИС на долговечность заключается в том, чтобы старение ускорилось, а процесс деградации параметров происходил так же, как и при нормальной работе схемы.

- При прогнозировании интенсивности отказов, используя результаты HTOL испытаний, необходимо знать Ea и TField. Энергия активации – параметр, который используют, чтобы выразить степень ускорения, связанную с температурой. Отдельные механизмы отказов сопровождаются уникальным значением энергии активации (JEDEC публикация № 122B.). Тем не менее, традиционные методы используют энергию активации 0.7 еВ, ее принято считать средней энергией активации для механизмов отказов, которые происходит во время срока службы устройств. Этот срок службы лежит за пределами ранних отказов (отказов во время приработки).

- Стандартные HTOL испытания не должны использоваться для прогнозирования интенсивности отказов, так как они дают оценки, которые являются слишком низкими.

- Исходя из расчетов интенсивность отказов в единицу времени (FIT) не зависит от технологии производства ИС. Таким образом, можно сделать вывод, что интенсивность отказов, рассчитанная по приведенному выше примеру, зависит только от количества испытуемых образцов, не принимая в расчет различия в технологии производства, механизмах отказов, ускоряющих факторах и т.д. Такой расчет интенсивности отказов, носит только количественный характер и не может в полной мере дать оценку, реальной надежности того или иного изделия.

Литература:

- Ивченко В.Г. Конструирование и технология ЭВМ. Конспект лекций. - /Таганрог: ТГРУ, Кафедра конструирования электронных средств. – 2001.

- Конструкторско-технологическое проектирование электронной аппаратуры: Учебник для вузов. – М.: Изд. МГТУ им. Н.Э. Баумана, 2002. – 528 с.

- Строгонов А.В. «Долговечность интегральных схем и производственные методы ее прогнозирования»: http://www.chipinfo.ru/literature/chipnews/200206/8.html.

- Mark White, Yuan Chen Jet Propulsion Laboratory Pasadena, California «Scaled CMOS Technology Reliability Users Guide», NASA Electronic Parts and Packaging (NEPP) Program Office of Safety and Mission Assurance, Copyright 2008. California Institute of Technology.

- М. Горлов, А. Строганов «Отбраковочные испытания как средство повышения надежности партий ИС»: Технологии в электронной промышленности, №1 2006.

- С.М. Никулин «Надежность Элементов Радиоэлектронной аппаратуры»: Москва «Энергия» 1979.

- F. Jensen, Fi. Jensen, P. Jensen, «Electronic Component Reliability: Fundamentals, Modeling, Evaluation, and Assurance». England, John Wiley & Sons, 1995.

- T. Smy, S. S. Winterton, «Simulation and analysis of electromigration failure distributions», ELSEVIER Microelectronics Reliability, vol. 34 No. 6, pp. 1047-1056, 1994.

- J.M. Huang, W. Yang, Z.J. Zhao «Interconnect damage by electromigration: experiment and numerical simulation», Acta Metallurgica, vol. 47 no. 1, pp. 89-99, Sep. 1998.

- JEDEC Solid State Technology Association, «Failure mechanisms and models for semiconductor devices», JEP122-B, Aug. 2003.

- Fen Chen, Rolf-Peter Vollertsen, Baozhen Li, Dave Harmon, Wing L. Lai, «A new empirical extrapolation method for time-dependent dielectric breakdown reliability projections of thin SiO2 and nitride–oxide dielectrics», ELSEVIER Microelectronics Reliability, vol. 42, pp. 335–341, 2002.

- J.H. Stathis, S. Zafar, «The negative bias temperature instability in MOS devices: A review», ELSEVIER Microelectronics Reliability, vol. 46, pp. 270–286, Sep. 2005. A. Teramoto, R. Kuroda, S. Sugawa, T. Ohmi, «Accurate negative bias temperature instability lifetime prediction based on hole injection», ELSEVIER Microelectronics Reliability, vol. 48, pp. 1649–1654, Aug. 2008.

- M. Karam, W. Fikry, H. Haddara, H. Ragai, «Implementation of hot-carrier reliability simulation in Eldo», in IEEE Int. Symp. On Circuits and Systems, vol. 5, 2001, pp. 515-518.

- J. B. Bernstein, M. Gurfinkel, X. Li, J. Walters, Y. Shapira, M. Talmor, «Electronic circuit reliability modeling», ELSEVIER Microelectronics Reliability, 2006, pp. 1957-1979.

- AVSI project AFE 17 reports.

- Edward Wyrwas, Lloyd Condra, Avshalom Hava, Accurate «Quantitative Physics-of-Failure Approach to Integrated Circuit Reliability».

- Зебрев Г.И. «Физические основы кремниевой наноэлектроники»: Учебное пособие. М.: МИФИ, 2008. — 288 с.

- М. Горлов, А. Строганов, А. Андреев «Входной контроль полупроводниковых изделий»: CHIP NEWS #3 (66), март, 2002.

- М. Горлов, А. Строганов, Д. Шацких «Технологические тренировки интегральных схем»: Компоненты и Технологии №4 2009.

- Edward J. Wyrwas and Joseph B. Bernstein «Quantitatively Analyzing the Performance of Integrated Circuits and Their Reliability» IEEE Instrumentation & Measurement Magazine February 2011.

- В. Романов «Количественная оценка надежности интегральных схем по результатам форсированных испытаний»: Электронные компоненты и системы 2003 октябрь № 10 (74).

- C.В. Гаврилов, О.Н. Гудкова «Логико-временной анализ надежности цифровых СБИС с учетом эффектов деградации NBTI и HCI» Учреждение Российской академии наук Институт проблем проектирования в микроэлектронике РАН, 2008.