В статье описываются основные особенности статических оперативных запоминающих устройств, принцип работы и основные виды неисправностей таких микросхем.

Ключевые слова: статические оперативные запоминающие устройства, триггеры, память, строки, столбцы, матрица, управляющие сигналы

Keywords: static random access memory, triggers, memory, rows, columns, matrix, control signals.

Статические оперативные запоминающие устройства на КМОП-структурах являются основой элементной базой, которая широко используется как в аппаратуре общего назначения, так и специальной.

Прогресс в технологии и схемотехнике в последние годы обеспечил устойчивый рост информационной емкости и быстродействия статических оперативных запоминающих устройств. Кроме таких достоинств, как малая потребляемая мощность в статическом и динамическом режимах, широкий диапазон допустимых изменений температуры и напряжения питания, высокая помехоустойчивость, к преимуществам статических оперативных запоминающих устройств можно отнести сравнительно высокое быстродействие, высокую стойкость к воздействию α-частиц, низкую температуру кристалла и, следовательно, более высокую надежность.

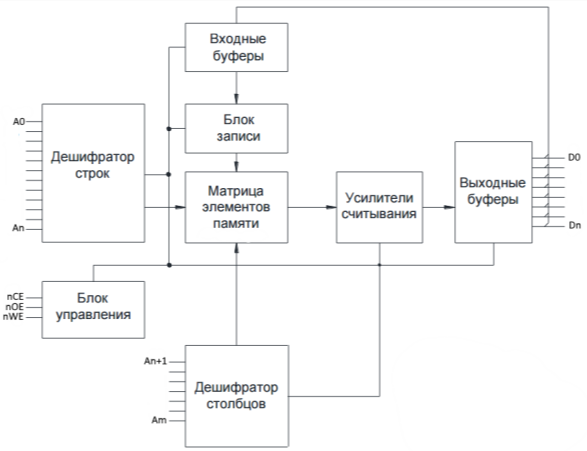

Типовая структурная схема статического оперативного запоминающего устройства представлена на рисунке 1. Главным элементом статического оперативного запоминающего устройства является матрица элементов памяти, объединённая в строки и столбцы. Выбор элемента памяти матрицы осуществляется с помощью адресных сигналов A, которые, как правило, делятся на дешифратор строк и столбцов. Управляющие сигналы nCE, nOE, nWE служат для управления режимами работы статического оперативного запоминающего устройства (хранение, считывание, запись).

Рис. 1. Структурная схема статического оперативного запоминающего устройства

Сигнал nWE определяет работу статического оперативного запоминающего устройства в режиме записи. Сигнал выбора микросхемы nCE служат для организации объединения статических оперативных запоминающих устройств по выходу и переводу невыбранной микросхемы памяти в режим хранения. Сигнал разрешения по выходу nOE разрешает работу выходных каскадов статического оперативного запоминающего устройства.

Выходные данные

Статическое оперативное запоминающее устройство состоит из триггеров. Триггеры могут находиться в двух состояниях: «выключен» или «включен». Переключение между состояниями проходят быстро, так как триггер не может хранить заряд. Но триггеры имеют более сложную технологию производства. Из-за этого цены на готовые устройства большие. Во-вторых, триггер, который состоит из группы транзисторов и связей между ними, занимает много места (на микроуровне), в результате статическое оперативное запоминающее устройство получается достаточно большим устройством.

Таким образом, основными тенденциями развития статических оперативных запоминающих устройств являются неуклонный рост информационной емкости и быстродействия, снижение удельных потребляемой мощности и стоимости, расширение номенклатуры универсальных статических оперативных запоминающих устройств, появление большого числа специализированных статических оперативных запоминающих устройств, в которых используются новые архитектурные решения.

Неисправность статического оперативного запоминающего устройства — это неправильная работа блока управления памяти или запоминающей матрицы, обнаруживающиеся в результате воздействия на оперативное запоминающее устройство тестовой последовательности двоичных сигналов [1].

1) Неисправности в запоминающей матрице[1]:

– «залипание»: содержимое конкретной ячейки всегда имеет одно и то же логическое значение;

– паразитная связь: операция записи или считывания в некоторую ячейку также воздействует на содержимое одной или более произвольно расположенных других ячеек, и взаимное воздействие между ячейками из-за паразитных эффектов;

– кодозависимая ошибка: ошибка с паразитной связью, которая ограничена соседними ячейками;

– короткое замыкание или обрыв цепи в разрядной или словарной шине: результаты при этих ошибках множественный доступ, искажение данных, недоступность строк ячеек.

2) Неисправность в дешифраторе адреса.

Недоступность одной или более ячеек памяти, или одновременный доступ ко многим ячейкам. Эта неисправность проявляется сама в невозможности сохранить данные в некотором регионе памяти, или в нарушении данных в не адресуемых ячейках в связи с операциями над другими ячейками.

3) Логическое чтение/запись.

Короткое замыкание, обрыв или залипание могут присутствовать в логике или каналах обмена данными, и в результате получается искажение данных.

4) Время восстановления записи.

При наличии этой неисправности, память не может подавать корректную информацию внутри заданного времени доступа, когда цикл записи непосредственно следует за операцией чтения. Хотя и время восстановления записи является АС параметром, неисправность определяется функциональным тестом, так как чувствительна к данным [2].

5) Контроль чувствительности усилителя.

Когда число операций случаются с одинаковыми данными, внезапное изменение значений, рассматриваемых данных может быть причиной проблем перехода в усилители. Эта неисправность типично относится к АС, но может быть выявлена при функциональном контроле [1].

В таблице 1 представлены типы неисправностей, которые приведены в зарубежной научной литературе [2].

Таблица 1

Неисправности оперативных запоминающих устройств

|

Наименование неисправности |

Аббревиатура |

Пояснение |

|

Неисправности одиночной ячейки |

||

|

StuckAt Fault |

SAF |

Ячейка памяти постоянно находится в состоянии логического нуля или логической единицы |

|

Stuck Open Fault |

SOF |

Ячейка не подсоединена (нет доступа) |

|

Transition Fault |

TF |

Ячейка, перейдя в состояние с определенным значением, не может совершить обратный переход |

|

Data Retention Fault |

DRF |

Ячейка переходит в стабильное состояние при отсутствии обращений к ней в течение некоторого времени |

|

Read Destructive Fault |

RDF |

Чтение из ячейки может изменить её содержимое |

|

Write Destructive Fault |

WDF |

Повторная запись в ячейку содержащегося в ней значения может изменить её содержимое |

|

Неисправности связки двух ячеек |

||

|

State CF |

CFst |

Ячейка принимает определённое значение при некотором значении другой ячейки |

|

Disturb CF |

CFds |

Ячейка принимает определённое значение при проведении операции чтения или записи с другой ячейкой |

|

Idempotent CF |

CFid |

Содержимое ячейки меняется при изменении значения другой ячейки |

|

Destructive Read CF |

CFdr |

Чтение из ячейки может изменить её содержимое при определённом значении другой ячейки |

|

Transition CF |

CFtr |

Невозможно изменить содержимое ячейки при определённом значении другой ячейки |

|

Write Destructive CF |

CFwd |

Повторная запись в ячейку содержащегося в ней значения может изменить её содержимое при определённом значении другой ячейки |

|

Neighborhood Pattern Sensitive Faults |

NPSF |

Ошибка в ячейке возникает при определённом состоянии ближайших к ней ячеек |

|

Неисправности управляющей логики |

||

|

Address Decoder Faults |

ADF |

Неисправности адресного декодера |

|

Write Enable/Output Enable/Chip Enable Fault |

WEF/OEF/CEF |

Сигнал WriteEnable/OutputEnable/ChipEnable находится постоянно в значении логического нуля или логической единицы или инвертирован |

|

Bitline/WordlineAccess Transistor Current Leakage Fault |

ATCLF |

Утечка тока транзистора доступа к bitline или dataline может послужить причиной неправильного чтения содержимого ячейки памяти |

Литература:

- Дерюгин А. А., Цыркин А. А., Красовский А. А. Применение интегральных микросхем памяти: Справочник [Текст] / А. А. Дерюгин, В. В. Цыркин, В. Е. Красовский. — М.: Радио и связь, 2009. — 232 с.;

- Уильямс Г. Б. Отладка микропроцессорных систем: Пер. с англ. [Текст] / Г. Б. Уильямс — М.: Энергоатомиздат, 2008. — 253 с.;