Коммутатором называется устройство для соединения нескольких узлов или сегментов в вычислительной технике. Данное устройство построено на основе последовательного соединения мультиплексора и демультиплексора.

Мультиплексором называют устройство, имеющее несколько сигнальных входов (D0, D1, D2, D3, D4, D5, D6, D7), один или более управляющих входов (A2, A1, A0) и один выход (OUT_MX). Таблица истинности восьмиканального мультиплексора представлена ниже.

Таблица 1

Таблица истинности восьмиканального мультиплексора

|

A2 |

A1 |

A0 |

OUT_MX |

|

0 |

0 |

0 |

D0 |

|

0 |

0 |

1 |

D1 |

|

0 |

1 |

0 |

D2 |

|

0 |

1 |

1 |

D3 |

|

1 |

0 |

0 |

D4 |

|

1 |

0 |

1 |

D5 |

|

1 |

1 |

0 |

D6 |

|

1 |

1 |

1 |

D7 |

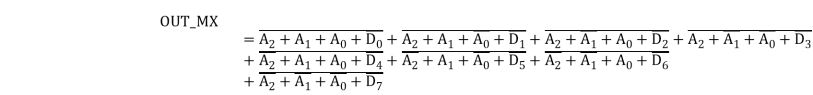

Исходя из таблицы № 1, получена логическая функция выхода мультиплексора.

Логическая схема, построенная на основе выше представленной функции представлена на рисунке 1.

Рис. 1. Логическая схема восьмиканального мультиплексора

Демультиплексором называют устройство, имеющее несколько сигнальных вход (D), один или более управляющих входов (A2, A1, A0) и несколько выходов (OUT, OUT1, OUT2, OUT3, OUT4, OUT5, OUT6, OUT7). Таблица истинности восьмиканального демультиплексора представлена ниже.

Таблица 2

Таблица истинности восьмиканального демультиплексора

|

A2 |

A1 |

A0 |

OUT0 |

OUT1 |

OUT2 |

OUT3 |

OUT4 |

OUT5 |

OUT6 |

OUT7 |

|

0 |

0 |

0 |

D |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

D |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

0 |

D |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

D |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

D |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

D |

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D |

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D |

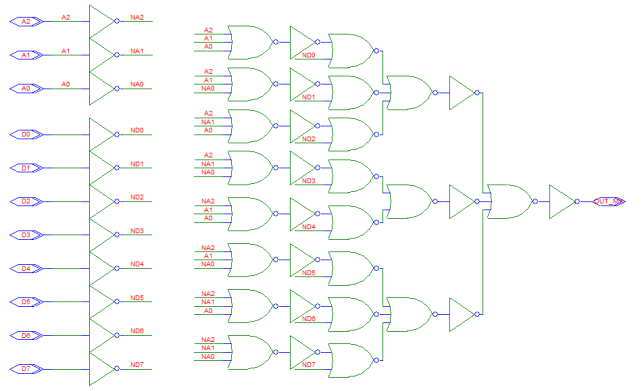

Исходя из таблицы № 2, получены логические функции выходов демультиплексора.

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

Логическая схема построенная на основе выше представленных функций представлена на рисунке 2.

Рис. 2. Логическая схема демультиплексора

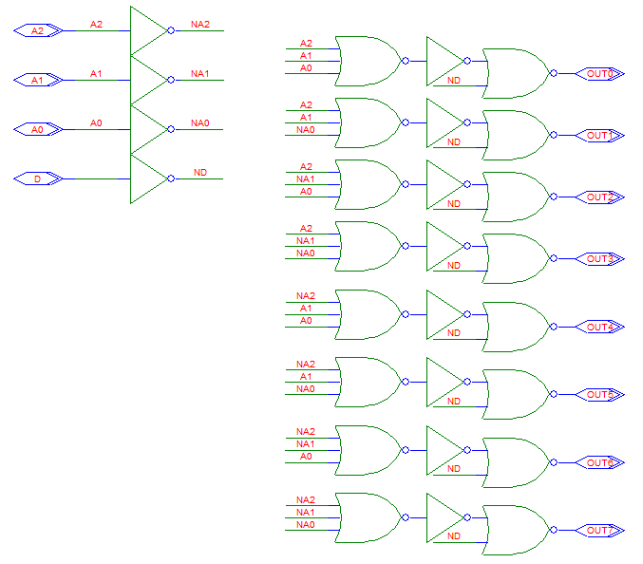

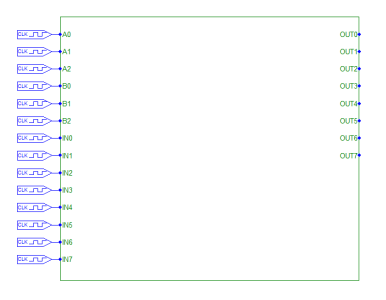

Результирующая логическая схема разрабатываемого устройства представлена на рисунке 3.

Рис. 3. Логическая схема разрабатываемого устройства

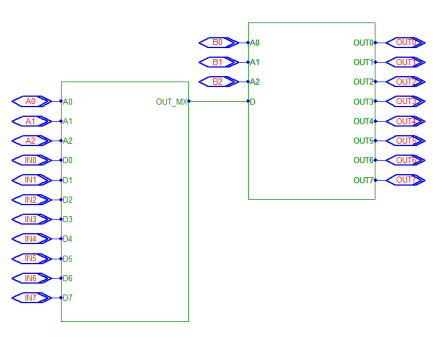

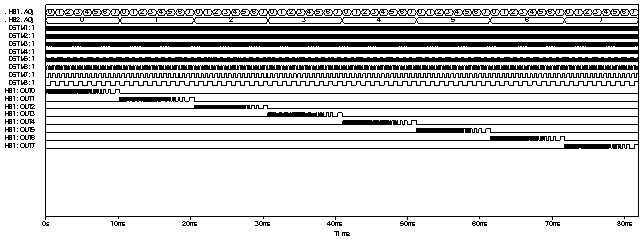

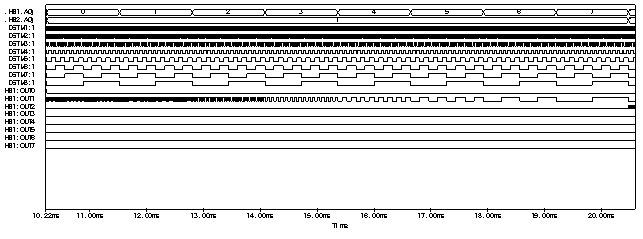

Схема логического моделирования и его результаты представлены на рисунках 4, 5 и 6.

Рис. 4. Схема логического моделирования разрабатываемого устройства

Рис. 5. Результаты логического моделирования разрабатываемого устройства

Рис. 6. Результаты логического моделирования разрабатываемого устройства

Максимальный логический путь сигнала Nmax=8.

Максимальный коэффициент разветвления Mcx=8.