В данной статье рассматривается тема метастабильного состояния триггера в цифровой схемотехнике. С подобной проблемой сталкивается большое количество начинающих разработчиков и программистов, потому как данного рода ошибка игнорируется компилятором и её невозможно отследить при моделировании и тестировании проекта в симуляторе. Таким образом, проект, безупречно работающий в среде моделирования, при переносе на аппаратную часть может работать иначе или же не работать вообще. На практическом примере демонстрируются важные для понимания темы вещи:

- Регистрация эффекта.

- Определение явления «метастабильность» в рамках цифровой схемотехники.

- Основные причины и ситуации возникновения.

- Способы устранения и анализ их эффективности.

- Практическая реализация.

Как было сказано ранее, метастабильность является сложной проблемой, потому как возникает на стадии аппаратной реализации, когда большая часть работы уже проделана. Продемонстрируем, в каком случае и как может проявить себя эффект метастабильности.

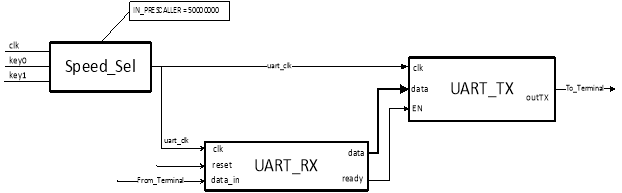

В качестве примера рассмотрим структурную схему устройства (рисунок 1).

Рис. 1. Структурная схема устройства

Данный блок реализует так называемый эхо-запрос, суть которого состоит в том, что данные, полученные со стороннего устройства возвращаются обратно в устройство, которое его отправляло. По тому, отличаются ли отправленные и полученные значения и то, с какой скоростью они пришли, можно судить, насколько исправно/эффективно работает система приёмопередатчика. В данном примере рассматривается популярный интерфейс UART, работающий по следующему алгоритму:

- Блок Speed_Sel обеспечивает тактирование блоков Uart.

- С терминала по линии data_in на устройство поступают данные.

- Блок UART_RX осуществляет преобразование в параллельный код и выставляет сигнал готовности ready.

- Определив готовность модуля приёмника, передатчик загружает данные и осуществляет обратное преобразование в последовательный канал, отправляя данные по линии OutTX в терминал.

Рассмотрим 2 варианта ввода данных для шифратора:

− Ввод данных через окно терминала (ручной ввод).

− Отправка двоичных файлов, содержащих набор команд (скрипты).

Ручной ввод данных производится непосредственно через терминал и не требует дополнительного программного обеспечения. Однако, этот способ существенно уступает по быстроте и удобству. В рамках тестирования эхо-запроса, не имеет значения, какая информация подвергаются передаче. Основная цель — полная идентичность отправленных и принятых данных. Проверка будет происходить в 2 режимах и с разным количеством передаваемых символов.

Тестирование модуля показало следующие результаты:

Таблица 1

Тестирование эхо-запроса

|

Количество символов |

Ручной ввод |

Двоичный файл |

|

1–10 |

успех |

успех |

|

10–50 |

успех |

успех |

|

50–100 |

неизвестно |

успех |

|

100–500 |

неизвестно |

неудача |

Как видно, при достаточно большом количестве символов, отправленные и принятые файлы не совпадают. Причиной этому стало такое явление как «метастабильное состояние триггера».

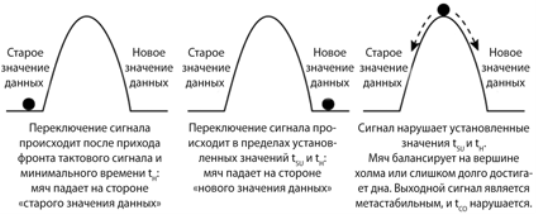

Метастабильность — это неспособность триггера достигнуть известного состояния в определенный момент времени. Когда триггер входит в метастабильное состояние, то невозможно предсказать ни уровень выходного напряжения элемента, ни период времени, за который этот выход перейдет к правильному уровню напряжения. Значит, находясь в таком состоянии, возможна передача неправильного сигнала в дальнейшую комбинационную логику. В литературных источниках зачастую иллюстрируют следующий пример (рисунок 2): «мячик» на последнем изображении находится в метастабильном состоянии, исход которого может отличаться каждый раз, вопреки заложенной логике программы.

Рис. 2. Пример из литературы

С чем же связаны причины возникновения подобного эффекта? На данный момент выделяют 3 основных причины, в которых может возникнуть ситуация метастабильности:

- Наличие асинхронных по отношению к тактовой частоте внешних событий.

- Временные задержки, вызванные большим расстоянием между элементами на микросхеме.

- Работа отдельных модулей внутри устройства на частотах, отличных от тактирования.

Для выделения причины рассмотрим структуру проекта, выполняющего эхо — запрос (рисунок 1). Во — первых, согласно некоторой математической формуле, был разработан модуль Speed_Sel, который является делителем входной частоты в 50 МГц. Значит, частота работы модулей UART_TX и UART_RX отличается от входной.

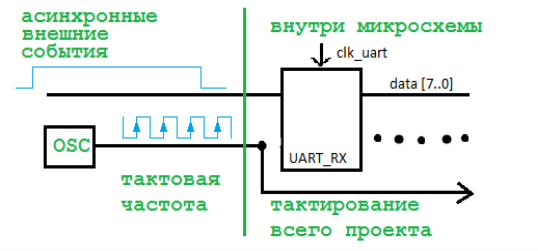

Во — вторых, следует обратить внимание на схему (рисунок 3). В нашем случае, под асинхронные события попадают:

- Входной сигнал Terminal_in с преобразователя USB — UART.

- Выходной сигнал To_terminal, является входом для преобразователя.

- Кнопки и переключатели отладочной платы.

Рис. 3. Тактирование модулей

Таким образом, имеем как минимум две из трёх возможных предпосылок к возникновению эффекта.

Способы устранения метастабильности.

Следует иметь ввиду, что невозможно полностью избавиться от данного эффекта. Можно лишь существенно снизить вероятность его возникновения. Для этого существует несколько популярных решений.

Первое — это введение регистров синхронизации на триггерах с отсутствием комбинаторной логики. К преимуществам можно отнести простоту реализации, а также небольшую затрату по аппаратным ресурсам. Основной недостаток — низкая эффективность в случае частого изменения сигнала (больше 2 перепадов за 10 тактов).

Второе — введение FIFO-логики с двумя тактовыми сигналами для хранения промежуточных значений сигналов или логики «рукопожатий» (hand-shaking logic). Существует специальный аппаратный блок — двухпортовая память с независимыми тактовыми сигналами (dual-port RAM). Это означает, что можно производить одновременно чтение и запись данных в память. Единственным ограничением является одновременное обращение на запись и чтение по одному и тому же адресу. Подобное действие может привести у неопределенному результату. На основе такого блока памяти создается модуль FIFO, который позволяет с одной стороны записывать данные из одного тактового домена, а с другой — забирать в другой тактовый домен. Заодно логика FIFO следит за тем, чтобы не происходило обращения к одной и той же ячейке памяти. К преимуществам можно отнести следующие:

− Наличие готовых, базовых решений у большинства САПРов.

− Обеспечивает достаточный уровень надежности и гибкую настройку (наличие информационных сигналов, количество хранимых слов, логика доступа и т. д.)

− Позволяет работать не только на единой частоте, но и на разных частотах для чтения и записи.

К недостаткам можно отнести:

− Практически всегда, большая затрата ресурсов, нежели триггеры.

− Необходимо продумывать логику взаимодействия между загрузкой и выгрузкой данных.

В — третьих, можно использовать стандартные блоки автоподстройки частоты (PLL). Это одно из самых надежных решений, которое уже включает в себя регистры синхронизации. Однако, в отличии от первых двух способов оно не настолько универсально и самое затратное по аппаратным ресурсам.

Практическая реализация.

В рамках рассматриваемого примера, было решено скомбинировать первый и второй способ. На рисунке 4 изображена схема после введения последовательных триггеров.

Рис. 4. Включение триггеров

Если первый триггер и «поймает» метастабильное состояние, то вероятно оно должно пройти к моменту фиксации сигнала во втором триггере. Понятно, что этот метод не избавляет от возможных проблем полностью, но зато он многократно уменьшает вероятность возникновения метастабильного состояния во втором триггере. После второго триггера мы можем с уверенностью считать, что сигнал будет всегда стабильным (либо «0», либо «1»).

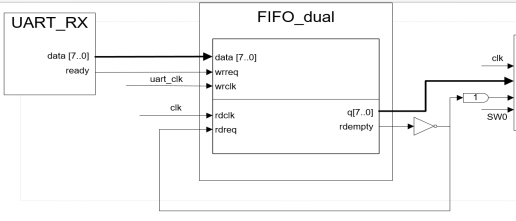

Схема стыковки блоков для реализации второго способа изображена на рисунке 5.

Рис. 5. Добавление блока FIFO

Описание сигналов блока FIFO_dual приведено в таблице ниже.

Таблица 2

Входы ивыходу FIFO_dual

|

Название |

Разрядность |

Тип |

Описание |

|

data |

8 |

вход |

шина данных |

|

wrclk |

1 |

вход |

сигнал тактирования для записи в память |

|

wrreq |

1 |

вход |

при 1, происходит запись данных в память |

|

rd_clk |

1 |

вход |

сигнал тактирования для чтения |

|

rdreq |

1 |

вход |

при 1, происходит чтение данных из памяти |

|

q |

8 |

выход |

шина выдачи данных по запросу |

|

rdempty |

1 |

выход |

флаг отсутствия данных в памяти |

На выходе rdempty стоит инвертор, заведенный обратной связью во вход rdreq. Таким образом, выполняется следующие условие: если память содержит пользовательские данные, то необходимо прочитать их. В противном случае, чтение не производить. Для обработки запроса на чтение, блоку FIFO необходимо дополнительный такт. Поэтому, для приёма корректных данных, необходимо задержать на 1 такт сигнал ready.

Пересоберем проект, включив в него необходимые изменения. При повторном тестировании, искажений данных не наблюдалось.

На этом, задачу можно считать выполненной и включать с внесенными изменениями как модуль, так и передатчик интерфейса.

Литература:

- Микушин А. В., Сажнев А. М., Сединин В. И. Цифровые устройства и микропроцессоры. — СПб.: БХВ-Петербург, 2010. — 823 с.