В статье авторы реализуют метод прямого цифрового синтеза гармонических сигналовна платах Altera DE2–115 и Data Conversion HSMC.

Ключевые слова: генерация, гармонический сигнал, ПЛИС, Quartus Prime, DE2–115, DAC5672, прямой цифровой синтез.

Плата DE2–115 и плата преобразования данных с разъемом HSMC, на которой установлен цифроаналоговый преобразователь будут подключены между собой по разъему HSMC. Напряжение питания разъема HSMC на плате DE2–115 контролируется элементом JP7 на котором защелкой устанавливается необходимое напряжение 3,3 В.

Для передачи сигнала в цифроаналоговый преобразователь будет использоваться канал Б (channel B). Для тактирования цифроаналогового преобразователя будут использоваться два вывода тактирования: прямой FPGA_CLK_B_P и обратный FPGA_CLK_B_N. Для выбора тактирования соответствующего канала преобразователя на элементе J17 платы преобразования данных устанавливаются защелки на контакты 1–3, 4–6. Для выбора сигнала тактирования выходного сигнала используется элемент J23 на плате преобразования данных. Соответственно выбранному каналу устанавливаются защелки на контакты 1–3, 4–6. Для подачи сигналов с платы DE2–115 на плату преобразования данных через разъем HSMC необходимо соотнести выводы этих разъемов на каждой из плат. Для правильного порядка назначения выводов необходимо проследить на схемах порядок подачи сигналов тактирования и данных по 14-разрядной шине данных, подключенной на плате к цифроаналоговому преобразователю. Чтобы назначить выводы подключения платы DE2–115 и платы расширения через разъем HSMC по схемам плат была составлена сводная таблица 1.

Таблица 1

Соотношение выводов разъема HSMC платы ПЛИС и платы расширения с ЦАП

|

DE2–115 |

DAC 5672 | ||

|

Сигнал на плате |

Выводы на плате |

Номер ножки на платах |

Сигнал на ЦАП |

|

RX D P8 |

PIN_R25 |

102 |

DB 13 |

|

RX D N8 |

PIN_R26 |

104 |

DB 12 |

|

RX D P9 |

PIN_T25 |

108 |

DB 11 |

|

RX D N9 |

PIN_T26 |

110 |

DB 10 |

|

RX D P10 |

PIN_U25 |

114 |

DB 9 |

|

RX D N10 |

PIN_U26 |

116 |

DB 8 |

|

RX D P11 |

PIN_L21 |

120 |

DB 7 |

|

RX D N11 |

PIN_L22 |

122 |

DB 6 |

|

RX D P12 |

PIN_N25 |

126 |

DB 5 |

|

RX D N12 |

PIN_N26 |

128 |

DB 4 |

|

RX D P13 |

PIN_P26 |

132 |

DB 3 |

|

RX D N13 |

PIN_P27 |

134 |

DB 2 |

|

RX D P14 |

PIN_P21 |

138 |

DB 1 |

|

RX D N14 |

PIN_R21 |

140 |

DB 0 |

|

HSMC CLKOUT P2 |

PIN_R39 |

155 |

FPGA CLK B P |

|

HSMC CLKOUT N2 |

PIN_R40 |

157 |

FPGA CLK B N |

Для получения синусоидального сигнала на вход ЦАП необходимо подать последовательность отсчетов функции y = sinx, следующих с частотой дискретизации f clk . Закон изменения функции y = sinx во времени сложен и цифровыми методами просто не реализуется. Поэтому наиболее подходящим методом формирования отсчетов функции y = sinx является табличный метод. Перекодировочная таблица (Look Up Table) размещается в ПЗУ [1].

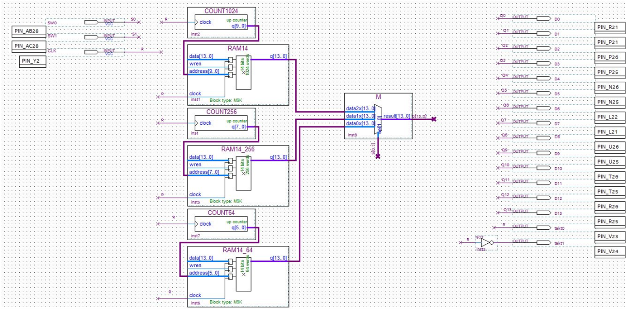

Для генерации сигнала была составлена схема в программном обеспечении Quartus Prime Lite. Спроектированная схема представлена на рисунке 1.

Рис. 1. Схема работы метода прямого цифрового синтеза гармонического сигнала в программе Quartus Prime Lite

Три вида сигнала представлены тремя парами счетчиков с памятью, размерностью в 1024, 256 и 64 отсчетов соответственно. Переключатели SW0 и SW1 управляют выходным сигналом и служат для переключения мультиплексора M. В зависимости от положения переключателей через мультиплексор на выход подаются 1024, 256 или 64 отсчета сигнала. На схеме счетчик импульсов и 14-ти разрядная память принимает импульсы от тактового генератора ПЛИС с вывода CLK. Счетчик импульсов поочередно переключает значения адреса в памяти, которая передает значения на 14-разрядную шину данных платы преобразования данных с цифроаналоговым преобразователем. Входы прямых и обратных тактовых импульсов цифроаналогового преобразователя также подключены к выводу тактового генератора CLK. Принимая цифровые отсчеты с памяти по каналу Б цифроаналоговый преобразователь выдает отсчеты гармонический сигнала на выход платы. Согласно составленной ранее таблице, назначаются выводы на схеме. Через разъем HSMC сигналы данных DB0 — DB13 передаются по каналу Б, прямой сигнал тактирования FPGA CLK B P и обратный FPGA CLK B N поступают на выходы тактирования цифроаналогового преобразователя, синхронизируя его работу с платой DE2–115.

Так как отсчеты из памяти подаются в цифроаналоговый преобразователь последовательно выходная частота генерируемого сигнала напрямую зависит от количества отсчетов в памяти. Выходная частота будет кратно меньше исходной частоты тактового генератора (50 МГц) в N раз, где N — количество отсчетов сигнала в памяти.

Отсчеты гармонического сигнала были предварительно сформированы в программе Microsoft Excel размером в 1024, 256 и 64 отсчета для исследования генерации сигнала. Предварительно были получены отсчеты угла, переведены в радианы, высчитан синус угла для каждого отсчета. Из-за специфики памяти значения в ячейках могут быть только целочисленными, поэтому полученные значения угла были переведены в положительные путем суммирования каждого отсчета с единицей, а после помножены до соответствующей размерности: исходя из размерности памяти максимальное значение 2 14 = 16384, отсчеты синуса в диапазоне от 0 до 2, следовательно каждая ячейка была умножена на 8192.

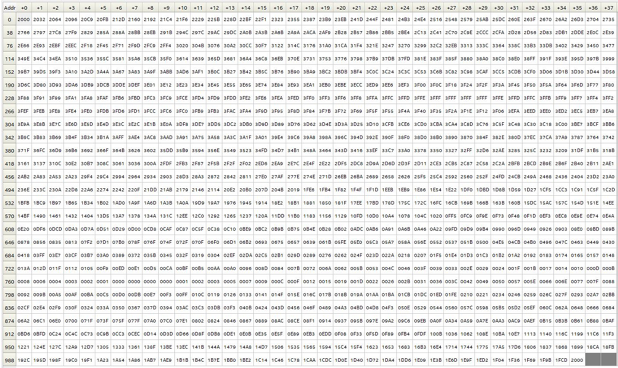

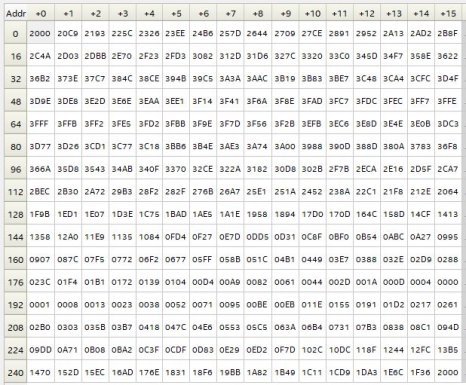

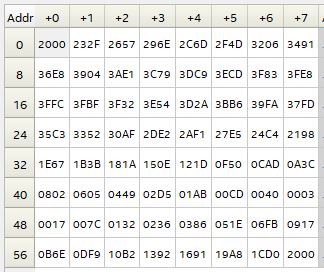

В память на схеме загружены предварительно полученные отсчеты синусоиды в виде 14-разрядного кода, с размерностью по 1024, 256 и 64 отсчетов. Значения ячеек памяти размером в 1024, 256 и 64 отсчета представлены на рисунках 2, 3, 4.

Рис. 2. Данные памяти размером в 1024 отсчета разрядностью 14 бит

Рис. 3. Данные памяти размером в 256 отсчетов разрядностью 14 бит

Рис. 4. Данные памяти размером в 64 отсчета разрядностью 14 бит

После успешной компиляции программы она загружается на плату для последующего тестирования. Выход канала Б цифроаналогового преобразователя подключается к осциллографу для вывода полученного сигнала. Оборудование для проверки работы схемы генерации представлено на рисунке 5.

Рис. 5. Плата DE2–115 и плата расширения с цифроаналоговым преобразователем DAC 5672

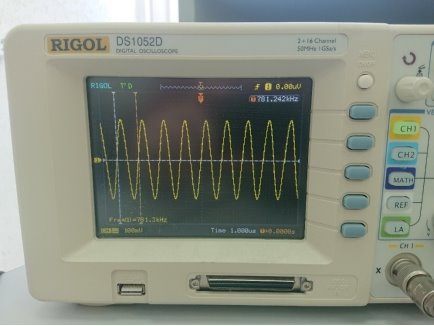

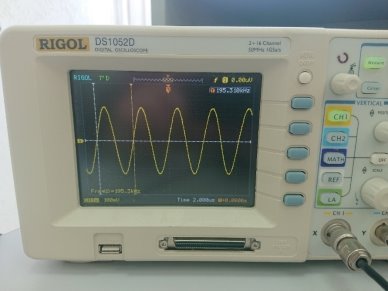

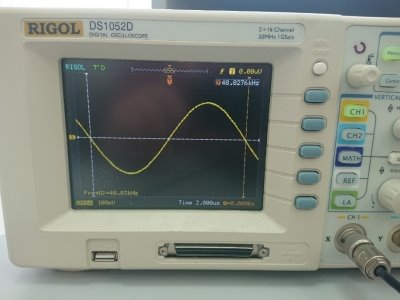

В результате работы схемы было получено представление гармонического синусоидального сигнала на осциллографе с частотой 800 кГц, 200 кГц и 50 кГц соответственно. Графики сигналов на осциллографе представлены на рисунках 6, 7, 8.

Рис. 6. Синусоидальный сигнал частотой 800 кГц

Рис. 7. Синусоидальный сигнал частотой 200 кГц

Рис. 8. Синусоидальный сигнал частотой 50 кГц

Литература:

- Тюрин В. А. Метод прямого цифрового синтеза в генераторах сигналов специальной формы SFG-2110 и АКИП-3410/3: учебно-методическое пособие / В. А. Тюрин. — Казань: Казанский федеральный университет, 2015. — 74 с.