Настоящая статья посвящена реализации одного из основных методов аналого-цифрового преобразования — метода поразрядного взвешивания. Разработана программная модель такого аналого-цифрового преобразователя в среде моделирования Matlab пакета расширения Simulink. Область применения разработанной модели — электронное образование с использованием вычислительной техники.

Ключевые слова: аналого-цифровое преобразование, электронные образовательные системы, компьютерное моделирование систем и устройств.

В настоящей статье представлен результат реализации аналого-цифрового преобразователя (АЦП) поразрядного взвешивания. Такие преобразователи являются базовыми при конструировании более сложных АЦП и находят широкое применение, поскольку системы управления ориентированы на передачу информации от источников (датчиков, измерительных преобразователей и т. д.) к получателям (исполнительным механизмам, регистраторам и т. д.) разной природы.

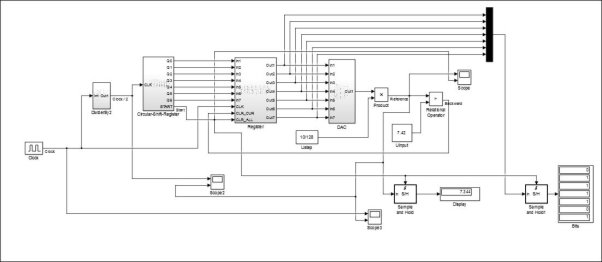

В качестве прототипа были использованы схемы из [1] и [2]. К методическим недостаткам при составлении описания к схемам прототипов можно указать недостаточно подробную схему формирующего регистра (Register на рис. 1).

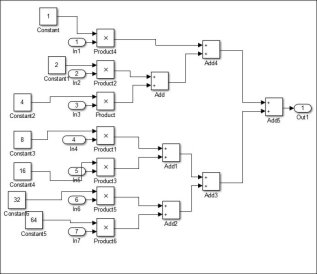

В данной работе реализована Simulink-модель АЦП поразрядного взвешивания с подробной разверткой всех подсистем: в первую очередь, формирующего регистра и далее кольцевого регистра, делителя частоты на два и вспомогательного ЦАП.

Рис. 1. Simulink-модель аналого-цифрового преобразователя поразрядного взвешивания

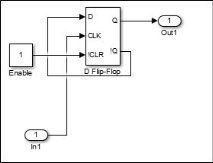

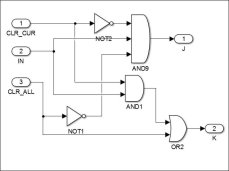

Рис. 2. Общеизвестная схема делителя частоты на два (DividerBy2 на рис. 1)

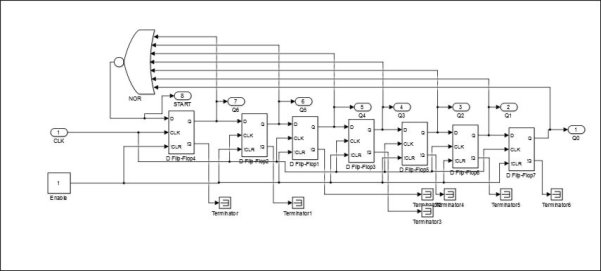

Рис. 3. Общеизвестная схема кольцевого регистра (Circular-Shift Register на рис. 1), построенная на D-триггерах

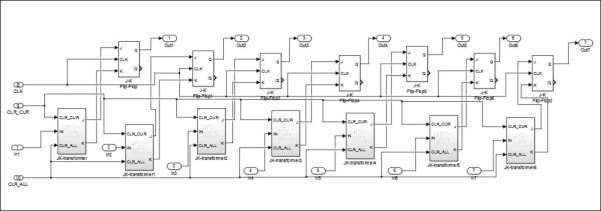

Рис. 4. Спроектированная авторами схема регистра, формирующего код согласно логике поразрядного взвешивания (Register на рис. 1)

Рис. 5. Схема вспомогательного цифро-аналогового преобразователя (DAC на рис. 1)

Рис. 6. Спроектированная авторами схема формирователя JK сигналов (JK-transformer, рис. 1) для JK-триггеров схемы управления формирующего регистра

Вход CLR_CUR предназначен для сброса в ноль текущего выхода формирующего регистра. При подаче на этот вход логической единицы на выходе J формируется логический ноль, а выход K при этом будет совпадать с входом IN. Согласно логике работы JK-триггеров такая комбинация JK-входов соответствует выходу триггера либо ноль (если K=1), либо предыдущему значению (если K=0). Таким образом, регистр либо сбрасывает текущее значение в ноль (если до сброса там была единица, т. е. K=IN=1), либо оставляет его незименным (если до сброса там был ноль, т. е. K=IN=0).

Вход CLR_ALL предназначен для безусловного сброса всех выходов регистра.

На вход IN поступает текущий бит с выхода кольцевого регистра.

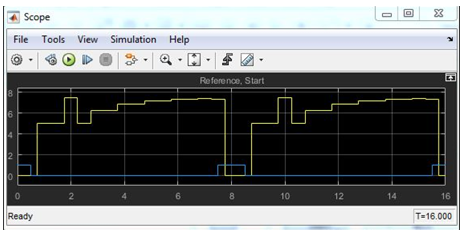

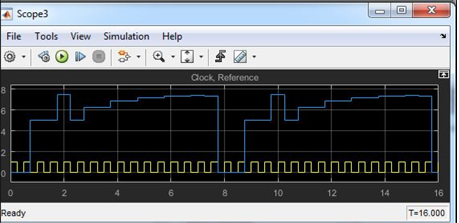

Рис. 7. Пример осциллограммы с выхода формирователя опорного напряжения (Reference на рис. 1), соответствующей двум циклам преобразования, а также импульса Start.

Передний фронт импульсов Start определяет момент выборки сформированного битового кода (Sample-and-Hold на рис. 1). Одновременно логический уровень 1 импульсов Start разрешает сброс формирующего регистра по заднему фронту тактовых импульсов (рис. 9, Clock).

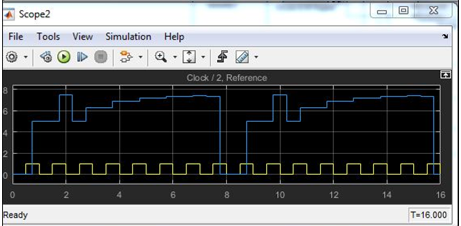

Рис. 8. Пример осциллограммы с выхода формирователя опорного напряжения (Reference на рис. 1), соответствующей двум циклам преобразования, а также импульса Clock/2.

Импульс Clock/2 соответствует тактовым импульсам Clock с частотой, поделенной на два делителем частоты (рис. 2).

Рис. 9. Пример осциллограммы с выхода формирователя опорного напряжения (Reference на рис. 1), соответствующей двум циклам преобразования, а также тактовых импульсов Clock.

Из рис. 9 видно, что сброс формирующего регистра происходит по заднему фронту тактовых импульсов.

Результаты проделанной работы будут внедрены в комплект компьютерных лабораторных работ на кафедре радиотехнических систем ТУСУРа (г. Томск).

Литература:

1. Акулиничев Ю. П., Теория электрической связи: Учебно-методическое пособие для проведения лабораторных работ и cамостоятельной работы [Электронный ресурс] / Акулиничев Ю. П. — Томск: ТУСУР, 2015. — 124 с. — Режим доступа: https://edu.tusur.ru/publications/5860.

2. Фрейман В. И. ПРОЕКТИРОВАНИЕ И ИССЛЕДОВАНИЕ МОДЕЛЕЙ АНАЛОГО-ЦИФРОВЫХ ПРЕОБРАЗОВАТЕЛЕЙ В СОСТАВЕ ЭЛЕМЕНТОВ И УСТРОЙСТВ СИСТЕМ УПРАВЛЕНИЯ // Современные наукоемкие технологии. — 2016. — № 8–2. — С. 270–274; URL: http://top-technologies.ru/ru/article/view?id=36142 (дата обращения: 14.05.2018).