Для упрощения применения микросхем flash-памяти NAND-типа они используются совместно со специальными микросхемами: «NAND-контроллерами». Эти контроллеры должны выполнять всю черновую работу по обслуживанию NAND-памяти: преобразование интерфейсов и протоколов, виртуализация адресации (с целью обхода сбойных ячеек), проверка и восстановление данных при чтении, забота о разном размере блоков стирания и записи, забота о периодическом обновлении записанных блоков (есть и такое требование), равномерное распределение нагрузки на секторы при записи (Wear leveling).

Однако задача равномерного распределения износа не обязательна, поэтому в самых дешевых изделиях ради экономии могут устанавливаться наиболее простые контроллеры. Такие flash-карты памяти и USB-брелоки быстро выйдут из строя при частой перезаписи, или при использовании файловой системы, отличной от той, на которую рассчитан контроллер. При необходимости очень частой записи данных на flash предпочтительно не изменять штатную файловую систему и использовать дорогие изделия с более износостойкой памятью (MLC вместо TLC, SLC вместо MLC) и качественными контроллерами [2].

На дорогие NAND-контроллеры также может возлагаться задача «ускорения» микросхем flash-памяти путём распределения данных одного файла по нескольким микросхемам. Время записи и чтения файла при этом сильно уменьшается [3].

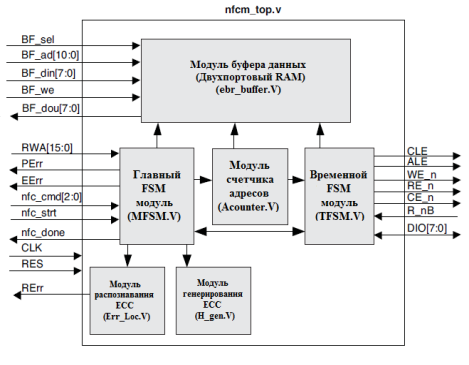

Главный FSM модуль (MFSM) и модуль синхронизации FSM (TFSM), содержат два конечных автомата состояний, они являются основными модулями контроллера. Эти два модуля взаимодействуют друг с другом. Конечный автомат в главном модуле FSM интерпретирует команды от хоста, а затем передает управляющие сигналы модулю синхронизации FSM. Конечный автомат в модуле FSM синхронизации создает все необходимые управляющие сигналы для NAND Flash, для выполнения повторяющихся задач со строгим временным регулированием, в соответствии с сигналами от основного модуля FSM. Модуль буфера данных (ebr_buffer) осуществляется внутренним двухпортовым RAM. Этот модуль используется в качестве буфера данных, когда хост записывает данные во Flash-память и считывает данные из Flash. Модуль адресного счетчика (Acounter) генерирует управляющие сигналы адреса, необходимые для модуля буфера данных на основе конечного автомата в основном модуле FSM. Модуль генератора ECC генерирует код коррекции ошибок (ECC) во время работы программы и сохраняет ECC код в NAND Flash. Модуль Детектор ECC использует этот ECC код во flash-памяти, чтобы обнаруживать ошибки в данных во время операции чтения.

Код команды должен быть записан в регистр команды перед каждой операцией на NAND Flash. Регистр команды не занимает адресуемой ячейки памяти. Этот регистр содержит команду, вместе с любыми адресами и информацией о данных, необходимых для выполнения команды. Для тестирования в рамках работы используется массив NAND flash микросхем Samsung K9F1G08R0A (с использованием обусловленных специфи- кацией команд: 001, 010, 100 и т. д.) [1].

Рис. 1. Блок-диаграмма контроллера.

Операция сброса

Когда хост устанавливает сигнал nfc_cmd на 011 и nfc_strt сигнал активен, контроллер инициирует операцию сброса. Конечный автомат в главном модуле FSM переходит из начального состояния в состояние, реализующее операцию сброса. В этом состоянии, главный модуль FSM передает управляющие сигналы к модулю синхронизации FSM для выполнения передачи кода команды FFh к NAND Flash. Когда передача кода команды выполнена, конечный автомат переключается в исходное состояние и ждет следующей операции.

Операция считывания идентификатора

Модуль инициирует операцию чтения ID, когда хост устанавливает сигнал nfc_cmd на 101 и nfc_strt сигнал активен. Конечный автомат в главном FSM модуле переключается из начального состояния в состояние, реализующее операцию чтения ID. Сначала конечный автомат записывает код команды 90h, а затем записывает код адреса 00h во Flash. И, наконец, конечный автомат считывает идентификационную информацию из Flash. Выход четырех циклов считывания последователен — код производителя (ECh), код устройства (для Samsung K9F1G08R0A, этот код A1h), любой код XXh, и четвертый цикл ID (для Samsung K9F1G08R0A, этот код 15h). Для каждого шага, конечный автомат вызывает модуль синхронизации FSM для генерирования соответствующих сигналов управления для доступа к NAND Flash. Когда операция чтения ID выполнена, конечный автомат переходи в исходное состояние (ожидание следующей операции).

Операция стирания блока

Контроллер инициирует операцию стирания, когда хост устанавливает сигнал nfc_cmd на 100, а сигнал nfc_strt активен. Конечный автомат в главном модуле FSM переходит из начального состояния в режим, осуществляющий операцию стирания блока. Во-первых, конечный автомат записывает код команды 60h во Flash, а затем записывает код адреса. Эти коды адреса должны быть установлены хостом заранее. После того как запись адреса закончена, конечный автомат записывает код команды d0h во Flash, а затем ожидает время tWB. tWB является параметром Samsung K9F1G08R0A (время перехода flash из состояния WE (write enable) в busy). Затем конечный автомат определяет сигнал R_nB. Если R_nB устанавливается в «1» на Flash, это указывает на то, что Flash завершило операцию стирания блока. Тогда конечный автомат посылает код команды чтения статуса 70H во flash-память, чтобы проверить, успешно ли прошла операция стирания блока.

Если результат, возвращаемый Flash, равен «1», это указывает на то, что операционный стирания блока прошла успешно. В противном случае, конечный автомат устанавливает EErr сигнал в «1», чтобы сообщить хосту, что операции блока стирания не удалось. Для каждого шага, конечный автомат вызывает модуль синхронизации FSM для генерирования соответствующих сигналов управления для доступа к NAND Flash с необходимыми требованиями синхронизации. Когда операция чтения состояния завершается, свичи конечного автомата возвращаются в начальное состояние, ожидая следующей операции.

Операция записи страницы

Устройство инициирует операцию записи страницы, когда хост устанавливает сигнал nfc_cmd в 001, а сигнал nfc_strt активен. Конечный автомат в главном модуле FSM переходит из начального состояния в состояние, осуществляющее работу операции записи страницы. Конечный автомат записывает код команды 80h и адрес кода во Flash, код адреса должен быть установлен хостом заранее. Затем конечный автомат передает 2048 байт во flash-память от буфера данных (двухпортовый RAM).

Адресные сигналы буфера данных генерируются модулем счетчика адресов на основании управляющих сигналов, посылаемых автоматом. Эта конструкция записывает 2048 байт во Flash в единицу времени. После записи 2048 байт, конечный автомат записывает 12 байт ECC (код коррекции ошибки), которые генерируются модулем генератора ЕСС во Flash.

Сначала конечный автомат записывает код команды 85h и адрес, а затем пишет 12 ECC байт во Flash. Когда все эти шаги будут завершены, конечный автомат записывает команду 10h во Flash. После tWB периода времени конечный автомат идентифицирует сигнал R_nB. Если R_nB устанавливается в «1» во Flash, это указывает на то, что Flash завершила операцию записи страницы. Затем конечный автомат посылает команду чтения состояния — код 70h во Flash, чтобы проверить, как прошла операция записи страницы. Если результат, возвращаемый Flash, «1» он указывает на то что операция прошла успешно. В противном случае, конечный автомат устанавливает PERR сигнал «1», чтобы указать хосту — операции ошибочна. Для каждого шага, конечный автомат вызывает модуль синхронизации FSM для генерации соответствующих управляющих сигналов для доступа к NAND Flash. Когда операция чтения состояния выполнена, автомат переходит в исходное состояние ожидания следующей операции.

Операция чтения страницы

Устройство инициирует операцию чтения страницы, когда хост устанавливает сигнал nfc_cmd в 010, и сигнал nfc_strt активен. Конечный автомат в главном модуле FSM переходит из начального состояния в состояние, реализующее операцию чтения страницы. Сначала конечный автомат записывает код команды 00h и адрес кода в Flash.

Затем конечный автомат записывает код команды 30h во Flash. По прошествии tWB конечный автомат определяет R_nB сигнал. Если R_nB устанавливается в «1» во Flash, это указывает на то, что Flash готова для передачи данных. Тогда конечный автомат начинает считывать 2048 байт из Flash и сохраняет эти байты в буфере данных (двухпортовый RAM).

Адресные сигналы буфера данных генерируются модулем счетчика адресов на основе сигналов управления, посланных конечным автоматом. После чтения 2048 байт, конечный автомат начинает ситывать 12 ECC байт из Flash. Сначала конечный автомат записывает код команды 05h и адрес во flash-память, а затем записывает код команды E0h во Flash. После того, как выполнены данные операции, конечный автомат считывает 12 байт ECC из Flash и вызывает модуль распознавания ECC для обнаружения ошибки. В случае обнаружения ошибки в байтах ECC, конечный автомат устанавливает RErr сигнал в «1». Для каждого шага, конечный автомат вызывает модуль синхронизации FSM для генерации соответствующих управляющих сигналов для доступа к NAND Flash. Когда операция чтения страницы выполнена, конечный автомат переходит в исходное состояние, ожидая следующей операции.

Используя вышеописанные алгоритмы, можно с легкостью сформировать наиболее распространенный контроллер flash-памяти с архитектурой организации запоминающих ячеек NAND.

Литература:

- NAND Flash Applications Design Guide, Toshiba America Electronic Components, Inc, 2003.

- Samsung Mass Producing 128Gb 3-bit MLC NAND Flash Kevin Parrish // Tom’s Hardware, 11 April 2013

- Edward Grochowski, Robert E.Fontana, Future Technology Challenges For NAND Flash and HDD Products // Flash Memory Summit, 2012 (англ.): slide 6 «Projected NAND Flash Memory Circuit Density Roadmap».