В последние 3-4 года в связи с увеличением потребности науки в высокоскоростных вычислениях возникла необходимость создания специализированных устройств, ускоряющих выполнение различных операций обработки данных. Проектирование специализированных устройств для решения узкого круга задач (либо одной задачи) нецелесообразно с экономической точки зрения. Такие устройства изготавливаются всего лишь в нескольких экземплярах, что весьма дорого. Большую практичность представляют реконфигурируемые устройства на базе программируемых логических интегральных схем (ПЛИС). Применение в устройствах программируемых микросхем позволяет существенно расширить количество решаемых задач на базе одного устройства.

Производители ПЛИС создают на базе своих микросхем аппаратные комплексы (Development kits) для решения различных задач. Основным назначением таких комплексов является макетирование разрабатываемых пользователем устройств. Как правило, они комплектуются большим объемом памяти, несколькими высокоскоростными портами ввода/вывода, множеством свободных пользовательских линий. Универсальность подобных решений делает их достаточно привлекательными для решения широкого круга задач, но высокая стоимость (от 1000$ и выше) ограничивает возможности по их приобретению.

В связи с высокой стоимостью зарубежных модулей, возникла необходимость создания аналогичного дешевого устройства. На кафедре «ЭВМ и Системы» Волгоградского государственного технического университета в 2007 году был разработан реконфигурируемый модуль P5116 на базе ПЛИС Altera Cyclone I с интерфейсом PCI. Цель создания модуля – исследование применения подобных устройств в высокоскоростных вычислениях. Основные характеристики модуля:

- Емкость ПЛИС – 12000 логических элементов;

- Встроенная оперативная память объемом 32 Мбайт;

- Интерфейс PCI (контроллер PLX PCI9054);

- Ввод/вывод: COM-порт, 20 пользовательских линий;

- 2 источника питания (от слота PCI или от внешнего блока питания 9В).

Конфигурирование ПЛИС Возможно двумя способами. При подаче питания на модуль происходит автоматическое конфигурирование ПЛИС из энергонезависимой памяти EEPROM. В процессе работы модуля возможна непосредственная прошивка ПЛИС через специальный порт.

Установленный на модуле контроллер шины PCI является промежуточным звеном между системным ПО и ПЛИС. Стандартный драйвер контроллера предоставляет набор функций собственного API и обеспечивает универсальный интерфейс работы с программируемой микросхемой. Преимуществом данного решения является возможность смены конфигурации модуля без перезагрузки ПК посредством непосредственной прошивки программируемой микросхемы. Также при использовании стандартного драйвера контроллера интерфейса PCI снимается необходимость переустановки драйверов после смены конфигурации ПЛИС. Это дает возможность упростить организацию программной части реконфигурируемого комплекса. Реализация взаимодействия интерфейсной части ПО с пользовательским устройством в ПЛИС сводится к созданию библиотеки функций. Таким образом есть возможность избежать повторной компиляции программ проекта при смене прошивки ПЛИС – достаточно будет лишь обратится к функциям из другой библиотеки.

В процессе работы с модулем P5116 были выявлены недостатки схемы. «Узким местом», снижающим производительность модуля является сам интерфейс PCI. При анализе работы модуля на тестовых задачах (алгоритм Гаусса, шифрация) время цикла работы устройства в ПЛИС было сравнимо со временем загрузки данных в память модуля и считывания результатов.

Табл. 1. Длительности фаз работы устройства для решения СЛАУ методом Гаусса.

|

Размер матрицы |

3 |

5 |

10 |

25 |

50 |

|

Время расчета, нс |

616 |

952 |

1792 |

4312 |

8512 |

|

Загрузка данных, нс |

9,6 |

24 |

88 |

520 |

2040 |

|

Выдача результатов, нс |

2,4 |

4 |

8 |

20 |

40 |

|

Суммарное время, нс |

628 |

980 |

1888 |

4852 |

10592 |

Как видно из таблицы 1, с увеличением размера исходной матрицы данных, время загрузки данных в память модуля сравнимо с временем обработки матрицы. Таким образом, общая производительность модуля снижалась на 15–20% от возможностей устройства в ПЛИС.

Новые серии микросхем программируемой логики позволяют уже на стадии проектирования решить большинство вышеупомянутых проблем. Микросхемы Altera четвертого поколения и Xilinx шестого поколения содержат большое количество интегрированных контроллеров и высокоскоростных приемопередатчиков. В частности:

- До 4 модулей PCI Express x4 с пропускной способностью5 Гбит/с;

- От 4 до 48 приёмо-передатчиков с пропускной способностью до 11,3 Гбит/с;

- Ethernet контроллеры 10/100/1000 Мбит/с;

- Контроллеры памяти DDR, DDR2, DDR3 обеспечивающие полосу пропускания до 12,8 Гбит/с;

- Полнодуплексные линии передачи данных до 1 Гбит/с.

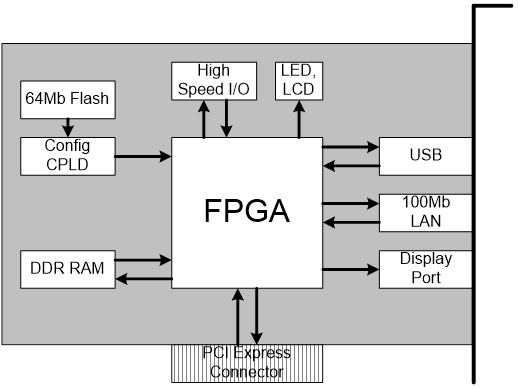

Наличие высокоскоростных линий передачи данных устраняет проблему задержек на загрузку и выгрузку данных. За счет интеграции контроллеров необходимых интерфейсов в микросхеме ПЛИС упрощается построение вычислительных модулей. На рис. 1 приведена общая схема реконфигурируемого модуля на базе чипов Altera или Xilinx последнего поколения. Данный вариант построения модулей на ПЛИС предполагает использование встроенных в ПЛИС контроллеров и реализацию необходимых протоколов на базе встроенных приемо-передатчиков.

Рис 1. Общая схема реконфигурируемого модуля на ПЛИС.

Такой подход позволяет сократить число используемых в проекте микросхем (в некоторых случаях вообще до одной – самой ПЛИС), что в свою очередь упрощает схему проекта и разводку печатной платы. Реализация внешних интерфейсов также упрощается – нет необходимости использовать микросхемы-посредники в качестве контроллеров соответствующих интерфейсов. Как правило, такие контроллеры требуют установки собственной конфигурационной ПЗУ и механизма конфигурирования. Проекты на новых FPGA конфигурируются непосредственно прошивкой самой ПЛИС или через дополнительную ПЛИС типа CPLD и Flash-память. В последнем случае возможно сохранение нескольких конфигураций платы на Flash-памяти. Конфигурирование же отдельных интерфейсов возможно непосредственно из системы, т.е. «на лету».

В настоящее время проходит стадию проектирования реконфигурируемый модуль на базе ПЛИС нового поколения Altera Cyclone IV. Новый проект обладает следующими характеристиками:

- Главная ПЛИС Altera Cyclone IV EP4CGX110 (108 тыс. Логических элементов, 5,4 кбит встроенной памяти, 280 умножителей 18*18, 8 приемо-передатчиков 3,125 Гбит/с);

- Интерфейс PCI-Express x4 с пропускной способностью 2,5 Гбит/с (v1.1);

- Встроенная оперативная память объемом 128 Мбайт;

- Конфигурационная флеш-память объемом 16 Мбайт;

- 10/100/1000BASE-T Ethernet;

- Пользовательские каналы приема и передачи данных пропускной способностью до 1 Гбит/с.

Проектируемый модуль имеет ряд преимуществ перед P5116. Во-первых, устанавливаемая ПЛИС обладает в 8 раз большей емкостью, что позволяет реализовывать проекты, обрабатывающие одновременно большое количество данных. Встроенные умножители 18*18 позволяют ускорить работу над числами с плавающей запятой. Тактовая частота работы ПЛИС поднята с 40 МГц до 100 МГц, что уже позволяет увеличить скорость работы пользовательских устройств в ПЛИС более чем в 2 раза. Установленная флеш-память большего объема позволяет хранить несколько конфигураций основной ПЛИС. Это позволяет ускорить процесс перенастройки вычислителя на решение другой задачи.

Модуль не оборудуется собственным LCD дисплеем, и разъемами для установки дополнительной памяти и дополнительными контроллерами. Это позволяет снизить стоимость модуля до 400-600$. Таким образом, изготовление таких модулей более выгодно с экономической точки зрения, чем закупка зарубежных аналогов, имеющих сравнимую производительность.

Одно из направлений применения реконфигурируемых модулей на базе ПЛИС связано с реализацией на них устройств «массового» использования. На современных материнских платах не устанавливается большое количество слотов расширения. Производители ограничиваются одним слотом PCI-Express x16, который в большинстве случаев занят более серьезным и производительным графическим акселератором, и одним – двумя слотами PCI-Express x4. Это очень ограничивает возможности по установке дополнительных сетевых адаптеров и, например, звуковой платы более высокого уровня.

Реконфигурируемый модуль может отчасти решить проблему нехватки слотов расширения. Возможности современных ПЛИС, описанные выше, позволяют реализовать на базе реконфигурируемого модуля следующие устройства:

- Сетевой адаптер;

- Графический ускоритель;

- Плата видеозахвата и обработки видеоинформации с цифровыми интерфейсами ввода/вывода видео и аудиопотока (HDMI, Fireware и т.д.);

- Плата цифровой обработки сигналов.

- Декодеры сигналов и шифрование (DVD, MPEG, AES и т.д.)

- Специализированные пользовательские устройства.

В заключении стоит отметить, что реконфигурируемые модули обеспечивают широкое применение модулей на ПЛИС, как в научной среде, так и в домашнем использовании. С точки зрения стоимости подобных решений универсальность микросхем FPGA и их множество позволяют строить модули, специализированные под выполнение каких-либо задач. Это позволяет удешевить «пользовательские» варианты модулей, установив в них бюджетные чипы, либо наоборот снабдить модуль высокоскоростными портами ввода/вывода и большими объемами памяти.

Литература:

1. Altera Cyclone IV FPGA Family. [Электронный ресурс] – Режим доступа: http://www.altera.com/products/devices/cyclone-iv/cyiv-index.jsp, свободный.

2. Xilinx Virtex-6 FPGA Family. [Электронный ресурс] – Режим доступа: – http://www.xilinx.com/products/virtex6/, свободный

3. Каляев И.А. Реконфигурируемые мультиконвеерные вычислительные структуры/ И.А. Каляев и др. – Ростов-на-дону: Издательство ЮНЦ РАН, 2008.