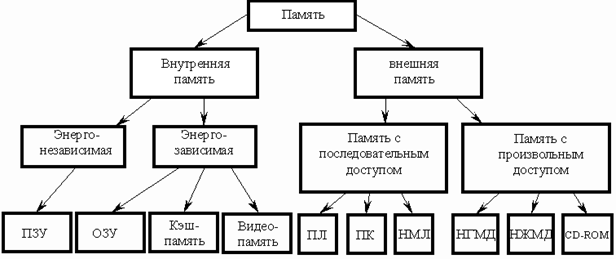

В современном мире, учитывая огромные объемы хранения данных и обработки большого количества информации, используются устройства, которые благодаря своей структуре способны выполнять операции связанные с записью, перезаписью и хранением данных. В зависимости от сферы применения запоминающие устройства используют того или иного типа (Рисунок 1).

Запоминающее устройство — устройство, основной функцией которого является запись и хранение информации. Принцип работы такого устройства заключается в любом физическом эффекте, который обеспечивает приведение системы к двум или более постоянным состояниям.

Рис. 1. Общая классификация запоминающих устройств[1]

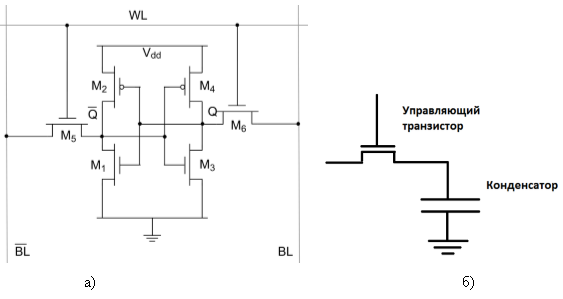

Статическая память (Рисунок 2а) является полупроводниковым типом памяти, в котором каждый следующий двоичный разряд находиться (хранится) в схеме с положительной обратной связью. Положительная обратная связь обеспечивает поддержку определенного состояния без регенерации, которая необходима в динамической памяти. Однако сохранение информации в статической памяти без перезаписи возможно только в том случае, если есть питание схемы так, как SRAM является энергозависимым видом памяти. К основным преимуществам SRAM можно отнести быстрый доступ, простоту в схемотехническом исполнении, частоты синхронизации памяти могут быть очень низкими. Недостатки данной архитектуры памяти заключаются в ее энергозависимости, в невысокой плотности ячеек вследствие чего цена производства выше, чем у DRAM (dynamic random access memory).

Рис. 2. Ячейки а) статической, б) динамической памяти: WL (Word Line) — линия управления транзисторами доступа М5, М6; BL (Bit Line) — битовые линии для записи и чтения данных

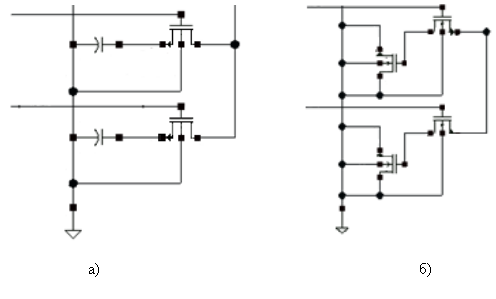

На физическом уровне динамическая память (Рисунок 2б) представляет собой матрицу ячеек, осуществляющих хранение информации. Ячейка состоит из адресного транзистора и элемента хранение «накопление» заряда. Элементов хранения одного бита информации может являться как конденсатор (Рисунок 3а), так и сам полевой транзистор с замкнутым стоком и истоком (Рисунок 3б), производя хранения информации в подзатворной емкости.

Рис. 3. Ячейки динамической памяти, построенные а) на управляющем транзисторе и конденсаторе, б) на двух транзисторах

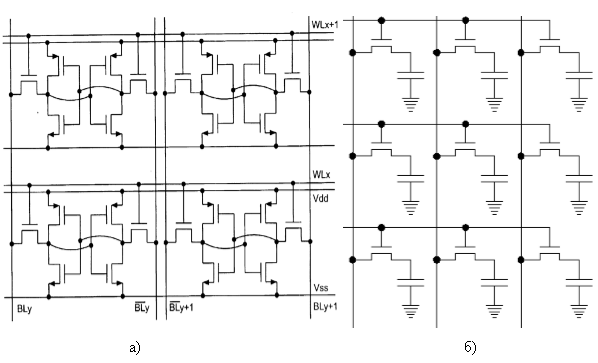

Рис. 4. Организация банка ячеек а) статической, б) динамической памяти

Динамическая память относительно статической является недорогой в изготовлении и имеет большую плотность компоновки ячеек (Рисунок 4). Стандартная ячейка динамической памяти обычно в своей структуре имеет два элемента, в то время как статическая минимум 6 элементов (транзисторов).

Недостатки динамической памяти заключаются в том, что она требует регенерацию записанных данных в ячейку и имеет относительно невысокое быстродействие.

Общая структура памяти спроизвольным доступом

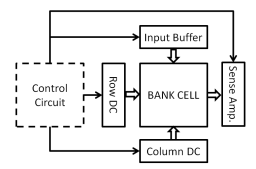

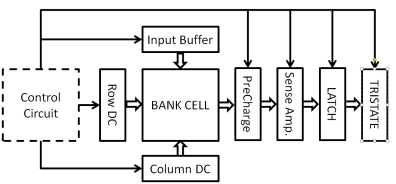

Упрощенная структура памяти с произвольным доступом имеет в своем составе следующие блоки (Рисунок 5):

– Дешифратор (Row, Column DC) — обеспечивает доступ к определенной ячейке, как правило, используют два дешифратора, которые организуют обращения к строкам и столбцам банка ячеек памяти.

– Банк ячеек памяти (Bank cell) — матрица ячеек для хранения информации.

– Триггер «защелка» (LATCH) — для установки двух битлайнов в противоположные состояния.

– Блок предзаряда битлайнов (PreCharge) — необходим для предзаряда битлайнов до половины питания, с целью уравнивания их напряжений, для организации корректного чтения данных с ячеек

– Дифференциальный усилитель (Sense Amp.) — необходим для усиления выходного сигнала

– Блок управления (Control Circuit), формирует сигналы, для обеспечения правильного алгоритма работы всей памяти (записи и считывания данных в ячейку памяти).

– Блок для организации высокоимпеданскного или Z-состояния (TRISTATE)

а)

б)

Рис. 5. Упрощенная структура а) статической, б) динамической памяти с произвольным доступом

Заключение

В современном мире практически ни одно электронное устройство не обходится без блоков памяти. Запоминающие устройства представляют собой сложно-функциональный блок, который выполняет функцию хранения и записи данных. В данной статье была рассмотрена общая классификация запоминающих устройств, статическая и динамическая память с произвольным доступом. Каждый из этих видов памяти имеет свои преимущества и недостатки, исходя из этого, определяется область применения запоминающих устройств.

Список использованных сокращений

– SRAM (static random access memory)

– DRAM (dynamic random access memory)

– ПЗУ — постоянное запоминающее устройство

– ОЗУ — оперативное-запоминающее устройство

– ПЛ — перфоленты

– ПК — перфокарты

– НМЛ — накопители на магнитных лентах

– НГМД — накопители на гибких магнитных дисках

– НЖМД — накопители на жестких магнитных дисках

Литература:

- Амосов В. В. — Схемотехника и средства проектирования цифровых устройств. БХВ-Петербург, 2012

- Бойко В. И., Гуржий А. Н. — Схемотехника электронных систем. Цифровые устройства. БХВ-Петербург, 2012

- Jason Cong — An interconnect centric design flow for nanometer technologies, Proceedings of IEEE, vol.89, 2009

- R. J. Baker, H. W. Li, D. E. Boyce. CMOS. Circuit Design, Layout, and Simulation, 2nd edition, 2011

- N. Weste,K. Eshragyan. Principles of CMOS VLSI Design. Adisson Wesley, 2013

- J. P. Uyemura. CMOS Logic Circuit Design. Kluwer Academic Publishers, 2014

- Vjay Gullapalli, Kaijani Shi — Hierarchical design techniques, Synopsys white paper, 2008

- Muzaffer A. Siddiqi — Dynamic RAM: Technology Advancements, CRC Press, 2012

- Pavlov A., Sachdev M. — CMOS SRAM Circuit Design and Parametric Test in Nano-Scaled Technologies: Process-Aware SRAM Design and Test, Springer Science & Business Media, 2008

[1] См. список сокращений в конце статьи