В настоящее время повсеместно и в космической технике в частности все большее распространение получают интеллектуальные датчики. Они отличаются от обычных датчиков наличием микропроцессора, который позволяет получать линейный сигнал от нелинейного датчика при помощи таблиц соответствия, хранящихся в памяти [1]. Также интеллектуальные датчики могут учитывать параметры окружающей среды с целью корректировки своих показаний. Это дает огромное преимущество интеллектуальному датчику перед обычным датчиком.

Выходной сигнал интеллектуального датчика имеет цифровой или аналоговый вид.

При использовании датчика с аналоговым выходом данные передаются на специальную регистрирующую аппаратуру.

Использование датчиков с цифровыми выходами имеет следующие преимущества:

· Минимизируется вероятность влияния различных помех на сигнал датчика.

· Приемная аппаратура имеет более простую структуру т.к. нет необходимости использовать цифро-аналоговый преобразователь (ЦАП).

Цифровые выходы интеллектуальных датчиков разных моделей передают информацию в различных форматах. Это создает неудобство для принимающей стороны: появляется необходимость использования различного приемного оборудования. Одним из вариантов решения данного вопроса является разработка универсального устройства (далее будем называть его устройством), которое осуществляет задачу перевода информации из стандарта, с которым работает интеллектуальный датчик, в другой стандарт, с которым работает приемное оборудование (в качестве приемного устройства может выступать ПК).

Такое устройство может быть реализовано на микросхемах (в полностью аппаратном виде), на микроконтроллере или на программируемой логической интегральной схеме (ПЛИС). Реализация на ПЛИС или на микроконтроллере имеет преимущество перед реализацией в полностью аппаратном виде: можно перепрограммировать (в случае с ПЛИС правильнее сказать переконфигурировать) данное устройство для добавления поддержки других стандартов входных сигналов. Микроконтроллеры чаще используют для выполнения сложных операций над небольшими объемами данных, в то время как ПЛИС используют для выполнения несложных операций над большими объемами данных. ПЛИС лучше подходит для выполнения задачи перевода сигнала информации из одного стандарта в другой.

Описание устройства.

Устройство разработано на базе ПЛИС фирмы ALTERA с использованием языка AHDL. Предусмотрена возможность передачи устройством сигнала интеллектуальному датчику с целью выдачи команд и возможности перепрограммирования датчика, имеющего перезаписываемое ПЗУ (постоянное запоминающее устройство).

Выбор режима работы устройства (стандарта входного и выходного сигнала) осуществляется двумя переключателями, смонтированными на корпусе устройства. Одним переключателем выбирается стандарт входного сигнала, другим – стандарт выходного сигнала. Переключатели осуществляют соединение контактов ПЛИС с контактами входных и выходных разъемов. Также переключателями осуществляется коммутация нужной комбинации контактов ПЛИС, по которой определяется режим ее работы (стандарт входного и выходного сигнала). «Распиновка» (сопоставление логических и физических входов и выходов ПЛИС) производится во время разработки проекта.

В устройстве реализована поддержка приема передачи данных по стандартам I2C, SPI, RS-232, RS-485, HART, USB (для приема и передачи данных на ПК) и параллельного восьмибитного кода, который используется в некотором специализированном оборудовании и является своеобразным логическим переходником в процессе преобразования сигнала из одного стандарта в другой.

В результате при наземных испытаниях изделий космической техники появляется возможность принимать информацию от различных типов датчиков, как на специализированное оборудование, так и на различные ПК. Оператор может подойти с ноутбуком, к которому подключено данное устройство, и проконтролировать показания конкретного датчика (на ноутбуке должно быть установлено специальное ПО).

Режим приема сигнала от датчика с интерфейсом I2C.

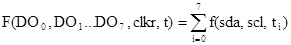

Рассмотрим режим работы устройства, при котором интеллектуальный датчик выдает сигнал в формате стандарта I2C [2], а на приемное оборудование передается параллельный восьмибитный код. В таком режиме устройство выполняет преобразование, описываемое формулой:

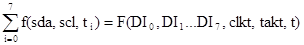

, (1)

, (1)

где sda, scl – входы устройства, описываемые стандартом I2C, ti – временной интервал считывания входного сигнала, DO0, DO1… DO7 – 8 информационных выходов устройства, clkr – командный выход устройства, t – временной интервал передачи выходного сигнала.

Устройство, работающее в данном режиме, будем называть приемником I2C.

Согласно стандарту I2C [2] передача и прием данных осуществляются по двум линиям: по линии синхронизации (SCL) и по линии данных (SDA). Обе линии имеют нагрузочные регистры, которые «подтягивают» их к уровню напряжения линии. Передатчик и приемник подключаются к линии как «открытый коллектор» по схеме «монтажное И»: уровень в лини высокий, если выходной транзистор закрыт, и низкий, если хотя бы один выходной транзистор на линии открыт [3].

Шина свободна, если уровень сигналов SDA и SCL высокий. Началом передачи данных является условие Start (обозначается как S) – подача низкого уровня на линию SDA при высоком уровне линии SCL. Перед этим передатчик должен убедиться, что шина свободна. При передаче данных состояние линии SDA может изменяться только при низком уровне SCL.

При передаче каждого бита передатчик должен установить нужный уровень SDA (соответствующий биту данных), установить на время такта передачи высокий уровень SCL. Приемник при получении данных должен считать уровень (бит данных) с линии SDA во время высоко уровня на линии SCL.

Каждая посылка данных состоит из 8-и бит, старший бит передается первым. После передачи посылки передатчик на один такт освобождает линию SDA для получения подтверждения. Приемник во время девятого такта формирует бит подтверждения (ACK), сигнализирующий о правильном приеме данных. Окончанием передачи данных является условие Stop (обозначается как P) – подача высокого уровня на линию SDA при высоком уровне линии SCL.

Условие Stop может и не вводится. В таком случае за битом ACK следует следующая посылка из восьми бит данных (так называемый Repeated Start).

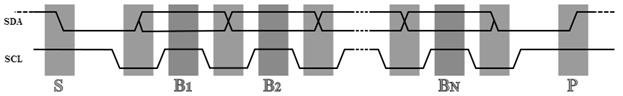

Временная диаграмма интерфейса I2C представлена на Рис. 1. На временной диаграмме показаны условия Start (S), Stop (P), биты данных (B1, B2…BN). Также показаны моменты изменения сигнала на линии SDA при низком уровне сигнала на линии SCL.

Рис. 1. Временная диаграмма интерфейса I2C

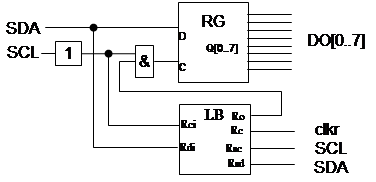

Структурная схема приемника I2C представлена на Рис. 2. На входы приёмника подаётся сигнал с линии SDA и линии SCL. Сигнал SDA подаётся на вход данных (D) сдвигового регистра (RG) и на вход Rdi логического блока (LB). Сигнал SCL подаётся через инвертор (1) на вход логического блока Rci и на логический элемент «И» (&). На второй вход элемента «И» подается сигнал с управляющего выхода LB (Ro). Сигнал с выхода логического элемента «И» подается на тактовый вход (C) регистра. На выходы приемника продается сигнал с восьми выходов регистра (данные, DO[0..7]) и командного выхода логического блока (команда на прием данных, clkr). Также логический блок имеет возможность управлять состоянием линий SCL и SDA.

Рис. 2. Структурная схема приемника I2C

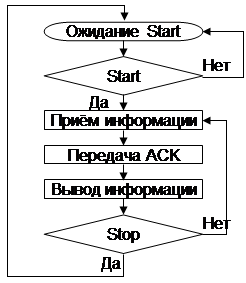

Основными составными элементами логического блока являются счетчик и таблица истинности. Логический блок управляет работой устройства в соответствии с алгоритмом, блок-схема которого представлена на Рис. 3. Изначально устройство находится в режиме ожидания приема информации. По состоянию линий SDA и SCL логический блок определяет срабатывание условия Star, выдает сигнал регистру на начало запоминания данных (после подачи логической единицы на Ro сигнал SCL начинает проходить через логическое «И»). После приема восьми бит данных логический блок дает команду считывающему устройству на прием данных и передает во входные линии (SDA, SCL) бит подтверждения успешного приема информации (ACK) путем управления состоянием входных транзисторов.

Одновременно с передачей ACK LB выдает на линию clkr сигнал принимающему оборудованию, по которому должно быть произведено считывание данных с выходов DO[0..7]. После чего отслеживается состояние линий SDA и SCL. В случае срабатывания условия Stop прием данных прекращается (на выход Ro подается логический ноль), а устройство переходит в режим ожидания. Если срабатывания условия Stop не обнаружено, то продолжается прием данных

Рис. 3. Блок-схема алгоритма работы приемника I2C

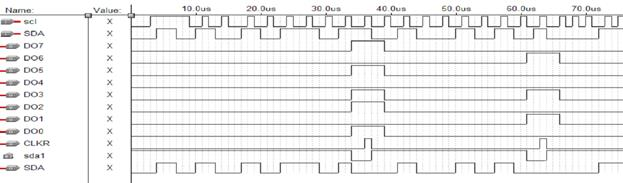

На Рис. 4. представлена временная диаграмма разработанного устройства, работающего в режиме приема информации от интеллектуального датчика с интерфейсом I2C и выдаче информации в виде параллельного восьмибитного кода на приемное устройство. Диаграмма выполнена в эмуляторе программы MAX Plus + 2 фирмы ALTERA. График sda1 на диаграмме отображает сигнал, передаваемый логическим блоком на входной транзистор линии SDA (фактически бит ACK). График SDA (второй сверху на диаграмме) – сигнал на входе линии SDA. График SDA (нижний на диаграмме) – результирующий сигнал на линии SDA (с учетом бита ACK). Остальные названия графиков на диаграмме соответствуют принятым ранее обозначениям. Показаны срабатывания условий Start, Repeated Start, Stop.

Рис. 4. Временная диаграмма работы приемника I2C

Режим передачи сигнала от датчика с интерфейсом I2C.

Работа устройства в режиме приема восьмибитного кода и передачи данных датчику с интерфейсом I2C описывается формулой:

, (2)

, (2)

где sda, scl – выходы устройства, описываемые стандартом I2C, ti – временные интервалы действия выходного сигнала, DI0, DI1… DI7 – 8 информационных входов устройства, clkt – командный вход устройства, takt – вход тактового сигнала, t – временной интервал передачи входного сигнала.

Устройство, работающее в данном режиме, будем называть передатчиком I2C.

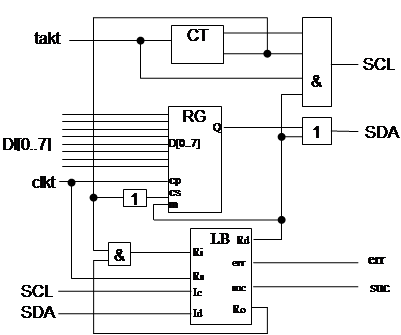

Данное преобразование является более сложным, чем преобразование, описываемое формулой (1), что приводит к затратам большего количества ресурсов. Структурная схема устройства в данном режиме работы представлена на Рис. 5.

Рис. 5. Структурная схема передатчика I2C.

На вход takt подается тактовый сигнал (тактовый генератор включен в устройство, сигнал с него подается на данный вход), на входы DI[0..7] подается воьмибитный код, который запоминается регистром RG во время подачи сигнала clkt на командный вход cp. Сигналы с устройства выдаются через выходы SCL и SDA (описаны стандартом I2C).

Тактовый сигнал передается на счетчик CT, который является делителем частоты. На основе нужной частоты формируется выходной сигнал SCL. Также на основе тактового сигнала (с преобразованной частотой) работает логический блок, а регистр RG преобразовывает параллельный код в последовательный (сигнал подается на вход cs, в этот момент регистр выполняет сдвиг данных, в результате чего на выход Q подается следующий бит). Сигнал, разрешающий выполнение сдвига данных (регистр должен выполнять сдвиг только во время передачи информации), подается на вход m регистра с логического блока LB (по данному сигналу регистр переключается в последовательный режим).

На схеме показаны линий SCL и SDA, подсоединенные ко входам логического блока Ic и Id – логический блок должен иметь возможность проверять состояние данных линий.

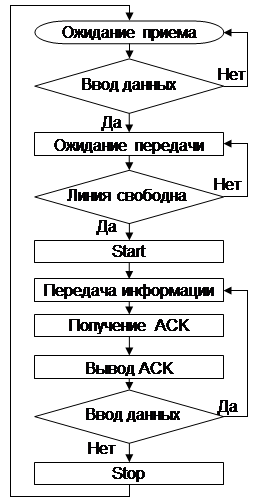

Блок-схема алгоритма работы устройства в режиме передачи сигнала I2C представлена на Рис. 6.

Рис. 6. Блок-схема алгоритма работы передатчика I2C

Логический блок в соответствии с алгоритмом управляет работой устройства. Первым этапом работы является ожидание ввода информации для передачи. Сигнал к вводу информации поступает по линии clkt. По этому сигналу логический блок подает на выход Ro логическую единицу, которая поступает на элемент «И» вместе с тактовым сигналом, в результате чего на вход Ri логического блока начинает поступать тактовый сигнал. Производится проверка состояния линии I2C (SCL и SDA), если линя свободна, начинается передача данных. Если же линия занята – опять производится проверка, пока линия не будет свободна.

Далее формируется условие Start (LB подает сигнал на Rd, который выводится в линию SDA), а регистр переводится в последовательный режим работы (тем же сигналом). Регистр, в соответствии с тактовым сигналом, сдвигает занесенные в него данные, и последовательно выдает их в линию SDA (происходит передача информации). При этом LB производит подсчет тактовых импульсов. Во время девятого тактового импульса LB проверяет приход ответного блока подтверждения (ACK) и выводит его передающему устройству, как свидетельство об успешной или неуспешной передаче блока данных. На следующем такте ожидается ввод блока данных (будет подан сигнал по линии clkt). Если данные не будут введены, формируется условие Stop, а регистр переводится в параллельный режим.

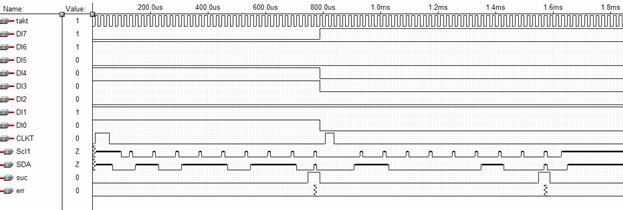

На Рис. 7. представлена временная диаграмма работы устройства в режиме передачи информации интеллектуальному датчику с интерфейсом I2C.

Рис. 7 . Временная диаграмма работы передатчика I2C

На диаграмме сигнал Scl1 соответствует сигналу в линии SCL. Сигналы suc и err передаются устройству, которое осуществляет ввод данных (передача логической единицы по линии err во время передачи логической единицы по линии suc свидетельствует о сбое при передаче данных).

Линии Scl1 и SDA на диаграмме часть времени находятся в Z – состоянии. Это позволяет логическому блоку анализировать состояние данных линий. В данные моменты времени уровень в линии будет высокий, если интеллектуальный датчик, как приемник сигнала I2C, не выдаст в линию низкий уровень сигнала (например, передавая бит ACK). В линию err во время передачи сигнала по линии suc передается состояние линии SDA. Но, часть этого промежутка времени линия SDA находятся в Z – состоянии, соответственно в эти моменты значение в линии err неизвестно.

Как отмечено выше, приемник и передатчик I2C подключены к линии как «открытый коллектор», благодаря чему уровни сигналов в линиях определяются состоянием входов/выходов обоих устройств. Тем самым достигается возможность передачи информации от приемника сигнала к передатчику, т.е. в обратную сторону – для получения бита подтверждения. При этом состояние линии err и линий SCL и SDA в любой момент времени определено однозначно.

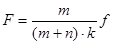

Следует отметить, что скорость работы передатчика I2C определяется частотой задающего генератора, которая должна соответствовать скорости передачи данных по шине I2C. Скорость передачи данных в данном случае определяется по формуле:

, (3)

, (3)

где F – скорость передачи данных (бит в секунду), f – частота работы генератора (герц), m – количество бит в одной посылке данных, n – количество проверочных бит на одну посылку данных, k – коэффициент (кратность) делителя частоты.

Учитывая, что  ,

,  ,

,  , получим:

, получим:  .

.

На скорость работы также накладывает ограничение сама ПЛИС, но их быстродействие довольно высоко для выполнения подобных задач.

Другим ограничивающим фактором является емкость ПЛИС. Для данного устройства требуется ПЛИС большой емкости (с большим количеством т.н. эквивалентных вентилей). Это связано с большим количеством поддерживаемых типов интерфейсов, а, следовательно, с большим количеством возможных режимов работы. Каждому интерфейсу входного и выходного сигнала соответствует своя конфигурация. Все эти конфигурации должны быть загружены в ПЛИС.

Литература:

1. Джексон Р. Г. Новейшие датчики Москва: Техносфера, 2007. — 384 с.

2. http://www.nxp.com/acrobat_download2/literature/9398/39340011.pdf

3. Гук М. Аппаратные интерфейсы ПК. Энциклопедия. — СПб.: Питер, 2002. — 528 с.: ил.